# ESSES 2003 European Summer School on Embedded Systems

### Lecture Notes Part IV

# Low Power Systems: Dynamic Voltage Scheduling

Editors: Ylva Boivie, Hans Hansson, Jane Kim, Sang Lyul Min

Västerås, July 21-25, 2003 ISSN 1404-3041 ISRN MDH-MRTC-104/2003-1-SE

# ESSES 2003 European Summer School on Embedded Systems

### Lecture Notes Part V

# Low Power Systems: Dynamic Voltage Scheduling

Editors: Ylva Boivie, Hans Hansson, Jane Kim, Sang Lyul Min

Västerås, July 21-25, 2003 ISSN 1404-3041 ISRN MDH-MRTC-104/2003-1-SE

## Dynamic Voltage Scaling for Hard Real-Time Systems

Jihong Kim

School of Computer Science & Engineering Seoul National University, Korea

### Dynamic Voltage Scaling for Hard Real-Time Systems

Jihong Kim

School of Computer Science & Engineering

Seoul National University

ESSES 2003 Västerås, Sweden

July 22, 2003

#### **Course Organization**

- Low-power systems 101

- Low-power binary encoding

- Power-aware compiler techniques

- Dynamic voltage scaling techniques

- OS-level DVS: Inter-Task DVS

- Compiler-level DVS: Intra-Task DVS

- Application-level DVS

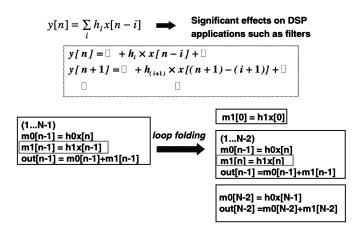

- Low-power convolution

#### Low Power S/W Research

Goal: Power-Aware Computing

Algorithms

Applications

Operating Systems

Compiler

Computer Organization

Transistor/Circuit/Logic

ESSES 2003 2003/7/22 (Jihong Kim)

5

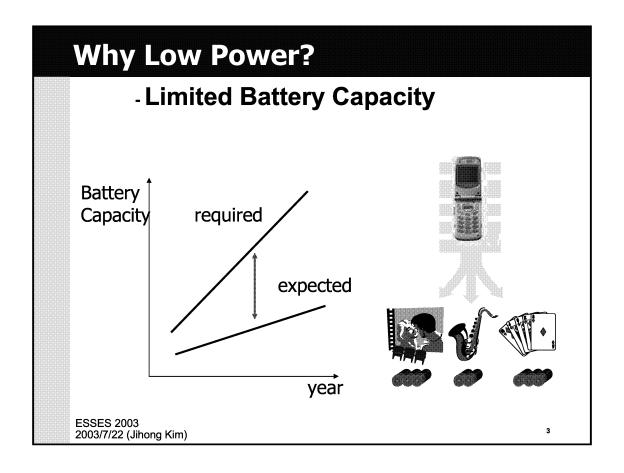

### Why S/W Techniques for Low Power?

- S/W techniques require no H/W modifications

- Many low-power H/W techniques require concurrent engineering between H/W and S/W.

- Examples: DPM, DVS, ...

- Efficiency of S/W Techniques are Critical for overall high energy efficiency

Algorithms Applications Operating Systems Compiler

ESSES 2003 2003/7/22 (Jihong Kim)

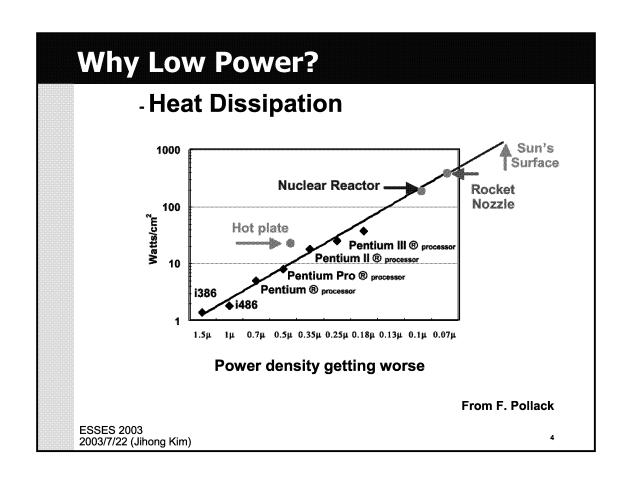

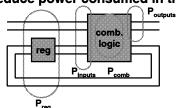

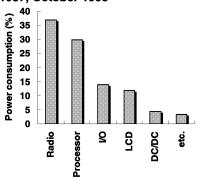

#### **Power Consumption in CMOS**

- **Dynamic Power Consumption**

- · Charging and discharging capacitors

- **Short circuit currents**

- Short circuit path between supply rails during switching

- Leakage current

- **Leaking diodes and transistors**

**ESSES 2003** 2003/7/22 (Jihong Kim)

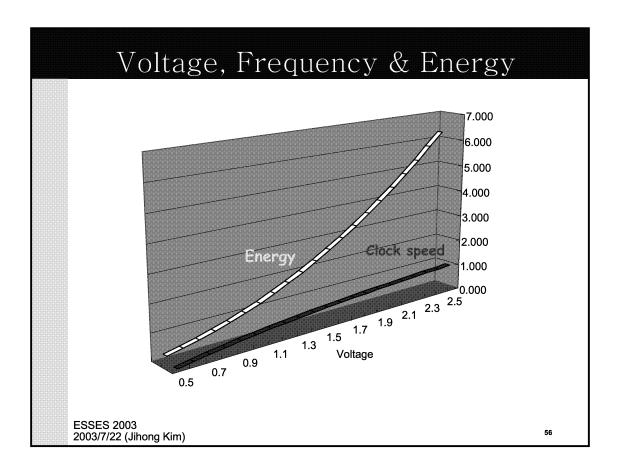

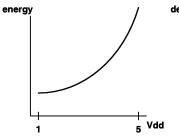

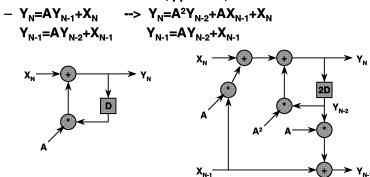

#### **Dynamic Power Consumption**

$$P_{dynamic} = K \times C_{out} \times V_{dd}^2 \times f$$

K: activity factor

C<sub>out</sub>: total chip capacitance V<sub>dd</sub><sup>2</sup>: supply voltage f: clock frequency

#### Reduce

- 1) switching activity

- 2) supply voltage

**ESSES 2003** 2003/7/22 (Jihong Kim)

#### Roadmap

- ✓ Low-power systems 101

- · Low-power binary encoding

- Power-aware compiler techniques

- Dynamic voltage scaling techniques

- intraDVS

- interDVS

- Low-power convolution

ESSES 2003 2003/7/22 (Jihong Kim)

,

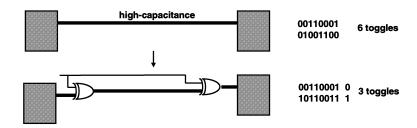

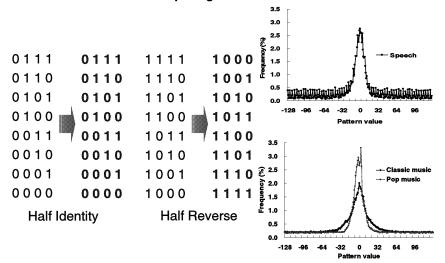

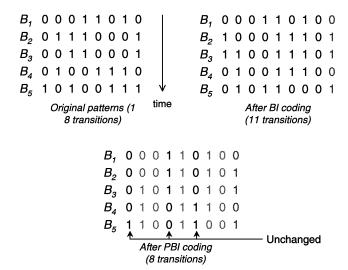

#### **Low Power Binary Encoding**

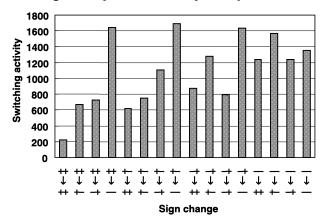

- Switching activity reduction

- Switching activity can account for over 90% of power dissipation of CMOS circuit. [Chandrakasan et al, '92]

- Goal of Low power binary encoding

- Modify the binary encoding/representation so that the switching activity is reduced.

- Target Areas:

- -Op-code field

- -Register field

- -Bus

ESSES 2003 2003/7/22 (Jihong Kim)

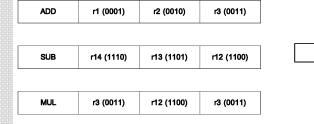

#### Register Relabeling

- Goal

- Assign register numbers to minimize the switching activities in register field

**Switching Activity**

Above : 20bit Right : 6bit

r2 (0010)

r3 (0011)

r12 (1100)

r8 (1000)

ADD

SUB

MUL r0 (0000) r1 (0001) r0 (0000)

ESSES 2003 2003/7/22 (Jihong Kim)

11

r0 (0000)

r1 (0001)

### Register Relabeling

- General Approach

- Collect the trace of register field usage information

- Construct the Register Field Transition Graph (RFTG)

Nodes: registers

Edges: transitions

- Edge weights: relative frequency of

corresponding edges

• Find new register number assignment that minimize the total bit changes.

ESSES 2003 2003/7/22 (Jihong Kim)

#### **Problem Formulation**

- A register field transition graph (RFTG)

- $G = (V,E,w) : V = V_{reg} \cup V_{imm}$

- A relabeling function

- find f:V<sub>reg</sub> → V<sub>reg</sub>, to minimize the following cost metric

$$\begin{split} P(G,f) &= \\ &\sum_{\substack{e = (v_1, v_2) \\ v_1, v_2 \in V_{reg}}} & w(e) \times h(f(v_1), f(v_2)) + \sum_{\substack{e = (v_1, v_2) \\ v_1 \in V_{reg} \\ v_2 \in V_{imm}}} & w(e) \times h(f(v_1), v_2) + \sum_{\substack{e = (v_1, v_2) \\ v_1 \in V_{imm} \\ v_2 \in V_{reg}}} & w(e) \times h(v_1, f(v_2)) \end{split}$$

where, w(e) is the weight of edge e

ESSES 2003 2003/7/22 (Jihong Kim)

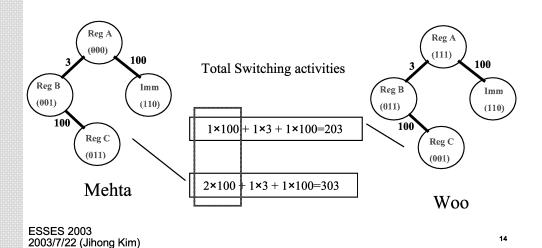

#### Register Relabeling

- Alternatives:

- Mehta's method: Immediate field not considered

- · Woo's method: Immediate field considered

#### Register Relabeling Heuristics

- Relabeling is a NP-hard problem

- NC<sub>2</sub> possible choices for each pair of exchanging candidates

- Slack-based heuristic [Woo, '01]

- Define slack value for each node (encoding)

$$slack(v_i, v_i) = [h(v_i, v_i) - 1] \cdot w(e)$$

- Exchange the encoding between most promising candidates until no more reduction is obtained from exchanging encoding

- Greedy method [Woo, '01]

- Exchange randomly but undo the exchange if no gain is obtained from it

ESSES 2003 2003/7/22 (Jihong Kim)

15

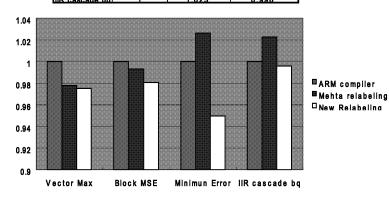

#### **Experiment (Switching Activity)**

- Simulation environment

- SimpleScalar simulator is used

- Benchmark

- SPEC95 int and SPEC95 fp

- UTDSP benchmark

- MPEG2 decoder with video only streams

- Result

- · % of switching activity

| Program               | No relabeling | Mehta relabelling | New relabelling |

|-----------------------|---------------|-------------------|-----------------|

| SPEC95 geometric mean | 1.0           | 0.96              | 0.91            |

| applu                 | 1.0           | 0.96              | 0.90            |

| compress              | 1.0           | 0.96              | 0.89            |

| gcc                   | 1.0           | 0.98              | 0.93            |

| UTDSP geometric mean  | 1.0           | 0.93              | 0.91            |

| adpcm                 | 1.0           | 0.93              | 0.92            |

| histogram             | 1.0           | 0.91              | 0.87            |

| turbo3d               | 1.0           | 0.96              | 0.93            |

| MPEG2 decoder         | 1.0           | 0.91              | 0.86            |

| Total average         | 1.0           | 0.94              | 0.89            |

ESSES 2003 2003/7/22 (Jihong Kim)

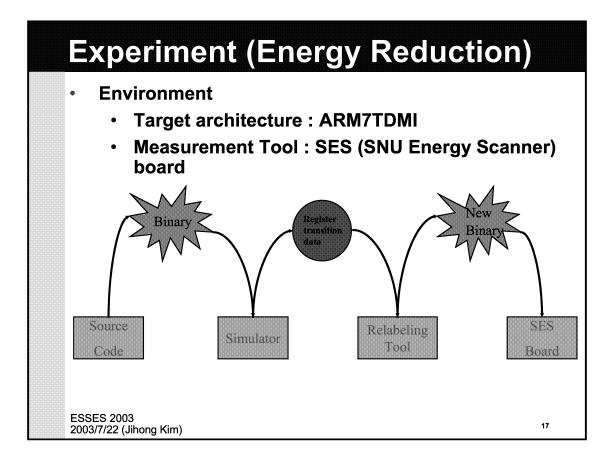

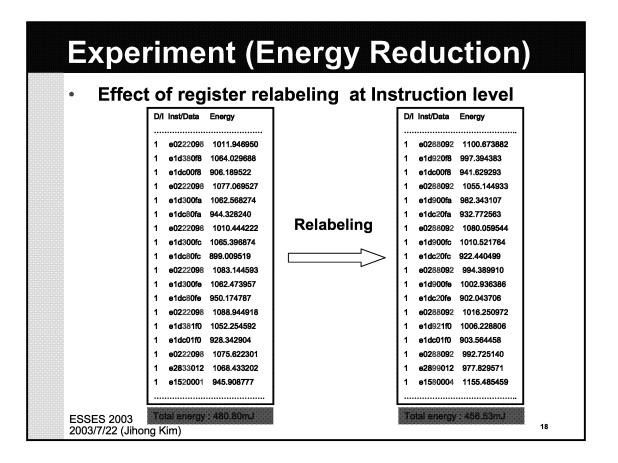

### **Experiment (Energy Reduction)**

- Result

- Benchmark : TI C6000 Benchmark

- Up to 5% energy reduction

| Programs       | ARM compiler | Mehta relabeling | New Relabeling |

|----------------|--------------|------------------|----------------|

| Vector Max     | 1            | 0.978            | 0.975          |

| Block MSF      | 1            | 0.993            | 0.981          |

| Minimun Error  | 1            | 1.026            | 0.950          |

| IID occorde ba | 1            | 1.023            | 0.006          |

ESSES 2003 2003/7/22 (Jihong Kim)

19

#### **Related Work**

- Register Relabeling

- Kandemir [Kandemir et al, '00]

- Similar to Mehta

- Give more time efficient heuristics

- Low power opcode encoding [Kim et al, '99]

ESSES 2003 2003/7/22 (Jihong Kim)

#### **Conclusion**

- Register relabeling with immediate values.

- Energy reduction without H/W modification

- Energy reduction with simple modification of binary codes

- Energy reduction up to 5% in CPU

ESSES 2003 2003/7/22 (Jihong Kim)

2

#### References

- Chandrakasan, T. Shyng, and R. W. Brodersen, "Low power CMOS Digital Design", IEEE Journal of Solid State Circuits, 1992

- S. Kim, and J. Kim, "Opcode Encoding for Low Power Instruction Fetch", IEE Electronic Letters, 1999

- H. Mehta, R. M. Owens, M. Irwin, R. Chen, and D. Ghosh,

"Techniques for Low Energy Software", Proc of ISLPED, 1997

- Ching-Long Su, Chi-Ying Tsui, and Alvin M. Despain, "Low Power Architecture Design and Compilation Techniques for High-Performance Processors", Proc of COMPCON, 1994

- M. Kandemir, N. Vijaykrishnan, M. J. Irwin, W. Ye, and I. Demirkiran, "Register relabeling: A post-compilation technique for energy reduction", Proc of the Workshop on Compilers and Operating Systems for Low Power, 2000

- S. Woo, J. Yoon, and J. Kim, "Low-Power Instruction Encoding Techniques", Proc of SoC Design Conference, 2001

ESSES 2003 2003/7/22 (Jihong Kim)

#### Roadmap

- ✓ Low-power systems 101

- √ Low-power binary encoding

- Power-aware compiler techniques

- Dynamic voltage scaling techniques

- intraDVS

- interDVS

- Low-power convolution

ESSES 2003 2003/7/22 (Jihong Kim)

23

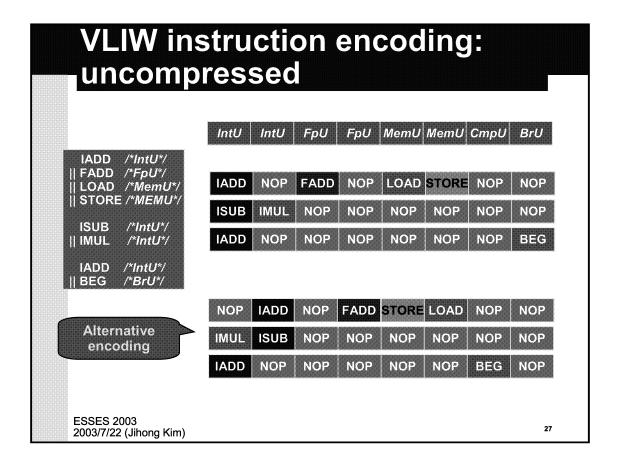

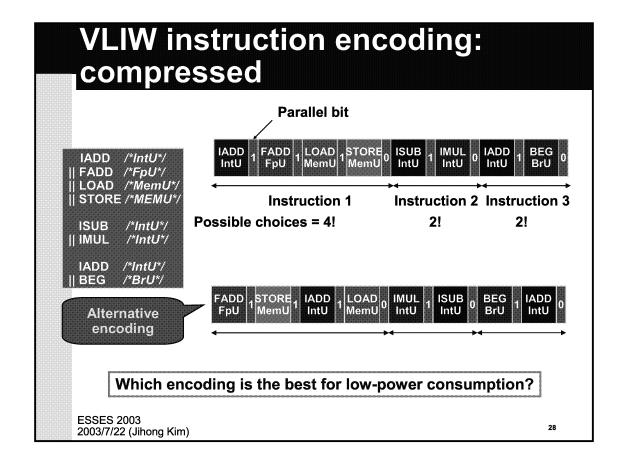

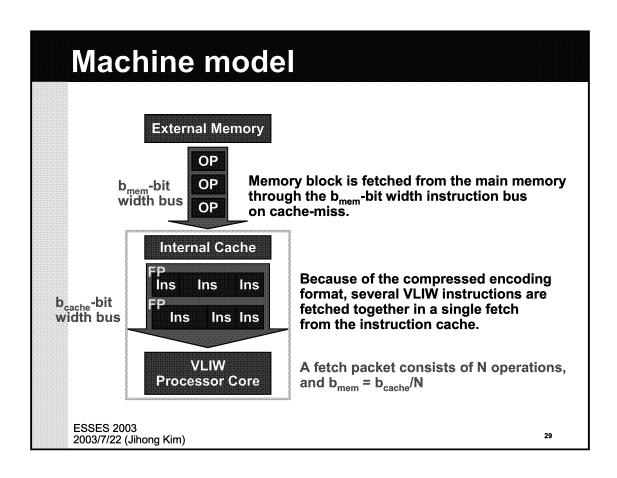

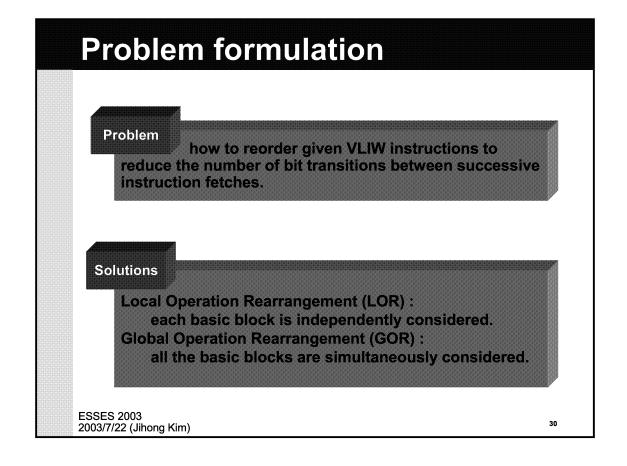

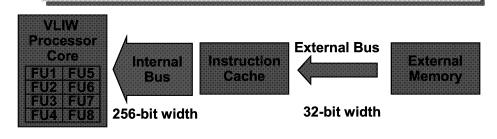

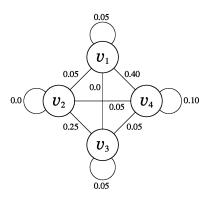

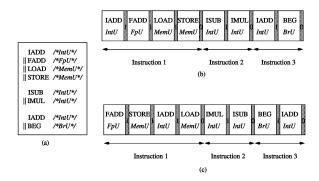

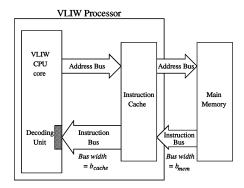

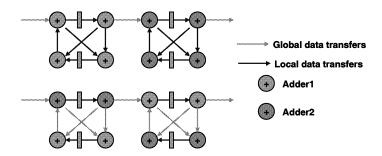

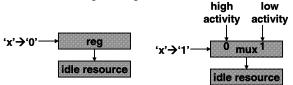

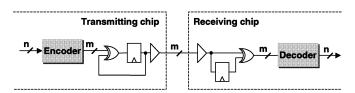

## Power-aware compiler techniques (for VLIW processors)

- Many mobile devices are designed using VLIW processors for high performance, which usually consume more power than single-issue processors.

- Operation rearrangement in VLIW instruction fetches

- · A post-past optimization technique

- Reduce switching activities by rearranging operations in each VLIW instruction.

- Battery-aware balanced modulo scheduling

- Effective battery utilization depends on current fluctuation

- Less fluctuation leads to longer battery lifetime

- Reduce power fluctuation

ESSES 2003 2003/7/22 (Jihong Kim)

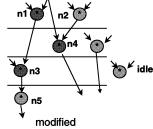

### Operation Rearrangement in VLIW Instruction Fetches

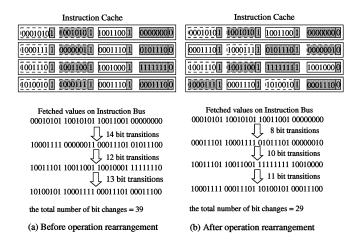

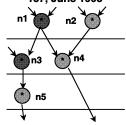

#### Basic idea **Instruction Cache Instruction Cache** 00010101 10010101 10011001 00000000 0001010<mark>1 1001010 1 1001100</mark>1 00000000 8 bit transitions 14 bit transitions 10001111 <mark>00000011 00011101 0101110</mark>0 00011101 10001111 01011101 <mark>0000001</mark>0 10 bit transitions 12 bit transitions 1001110<mark>1 |</mark>1001100<mark>1 |1001000</mark>1 |11111110 13 bit transitions 11 bit transitions 1010010 1 1000111 1 0001110 1 00011100 1000111 00011101 10100101 00011100 **Total 39 bit transitions Total 29 bit transitions** (a) Before operation rearrangement (b) After operation rearrangement The total # of bit changes are reduced by 25% **ESSES 2003** 26 2003/7/22 (Jihong Kim)

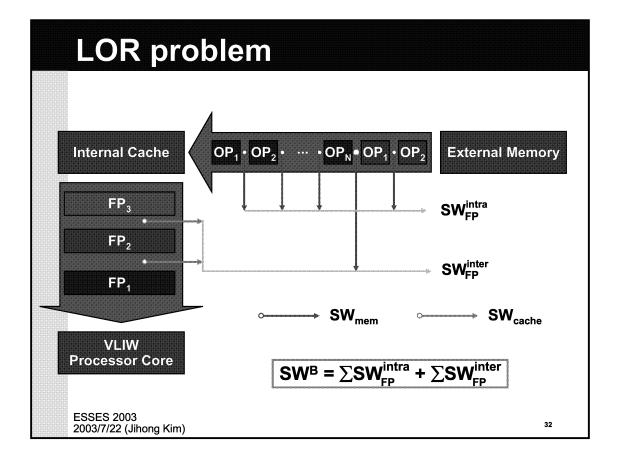

#### LOR problem

SW<sup>B</sup> = SW<sup>B</sup><sub>cache</sub> +

$$\alpha$$

•SW<sup>B</sup><sub>mem</sub>

$\alpha$  is the load capacitance ratio of the external instruction bus to the internal instruction bus.

SW<sub>cache</sub> is the number of bit changes at the internal instruction bus.

SW<sub>mem</sub> is the number of bit changes at the external instruction bus.

ESSES 2003 2003/7/22 (Jihong Kim)

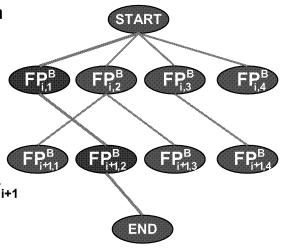

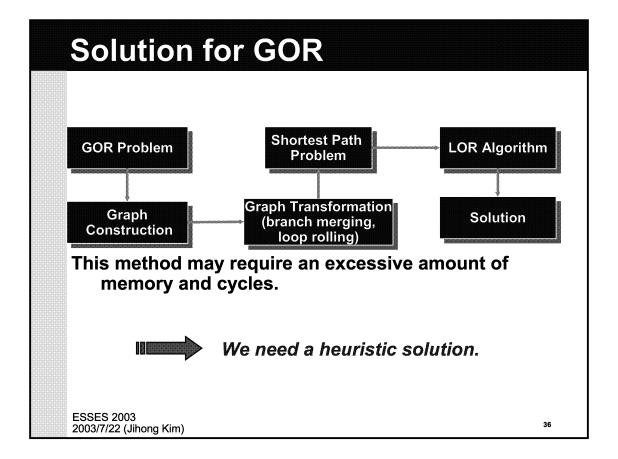

#### **Solution for LOR**

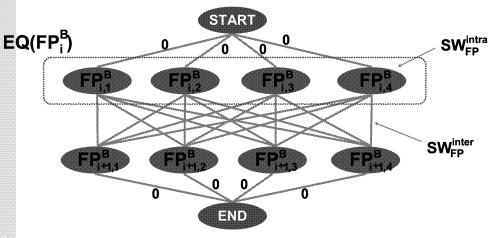

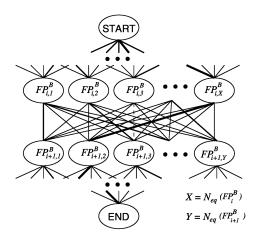

EQ(FP<sub>i</sub><sup>B</sup>): The set of equivalent fetch packets of FP<sub>i</sub><sup>B</sup>.

ESSES 2003 2003/7/22 (Jihong Kim)

33

#### Solution for LOR

- We find the shortest path from START to END, which is the solution of operation rearrangement to minimize the SW<sup>B</sup>

- A node v<sub>i+1</sub> in graph finds the node v<sub>i</sub> through which the shortest path from START to the node v<sub>i+1</sub> should pass.

ESSES 2003 2003/7/22 (Jihong Kim)

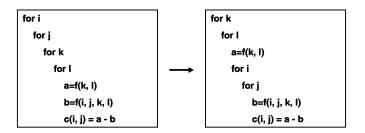

#### **GOR** problem

- All the basic blocks in a program are simultaneously considered

- how many times each basic block is executed.

- how often each basic block experiences cache misses.

- how basic blocks are related each other.

$$SW^S = \sum \sum SW_{BB}^{inter}(bb_i,bb_j) + \sum SW_{BB}^{intra}(bb_i)$$

SW<sup>inter</sup><sub>BB</sub> and SW<sup>intra</sup><sub>BB</sub> is represented by SW<sup>inter</sup><sub>FP</sub>,

SW<sup>intra</sup><sub>FP</sub>, weight of each basic block, and cache miss rate.

ESSES 2003 2003/7/22 (Jihong Kim)

#### **Heuristic for GOR**

- All the basic blocks are not equally treated.

- Basic blocks with larger effects on the total switching activity are more thoroughly reordered than ones with smaller effects.

- Not all the equivalent basic blocks in EQ(bb<sub>i</sub>) are tried to find an optimal solution.

- Only N<sub>cand</sub> equivalent basic blocks are created and included in graph.

ESSES 2003 2003/7/22 (Jihong Kim)

37

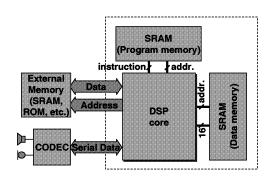

#### **Experiment**

#### TMS320C6201

- Fixed-point DSP

- VLIW processor that can specify eight 32-bit operations in a single 256-bit instruction.

- Use a compressed encoding

ESSES 2003 2003/7/22 (Jihong Kim)

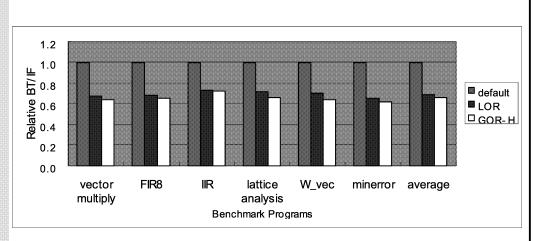

#### **Experimental results**

For our benchmark programs, the bit transitions was reduced by 34% on an average.

ESSES 2003 2003/7/22 (Jihong Kim)

39

#### **Conclusion**

- Described a post-pass optimal operation rearrangement method for low-power VLIW instruction fetch.

- The switching activity was reduced by 34% on an average.

- Future works

- The phase-ordering problem between the operation rearrangement and other compiler optimization steps.

- Operation rearrangement problem in superscalar processors.

ESSES 2003 2003/7/22 (Jihong Kim)

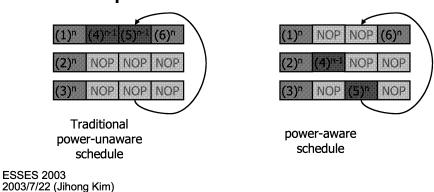

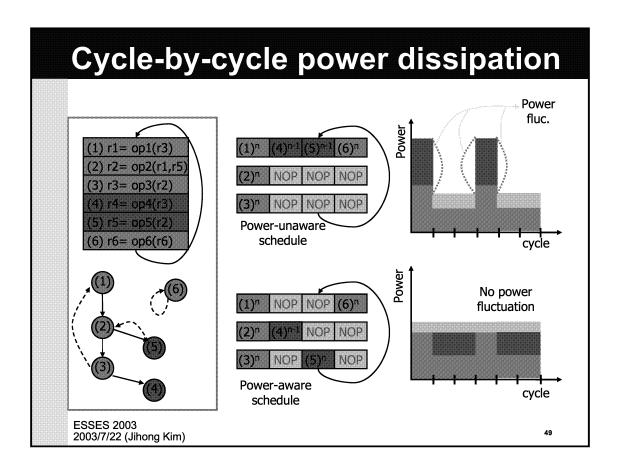

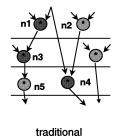

### **Battery-Aware Modulo Scheduling for VLIW Processors**

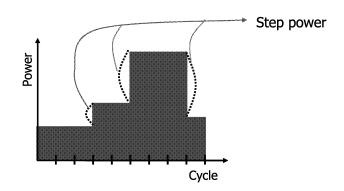

#### **Power Fluctuation**

- In VLIW processors, power fluctuation significantly depends on the parallel schedule generated by compilers

- Closely related to battery-lifetime

- As current fluctuation becomes larger, battery lifetime becomes shorter

- · Battery-aware balanced modulo scheduling

- Traditional power-unaware modulo scheduling algorithm is modified so that the power fluctuation is reduced

- No performance loss nor additional energy consumption

#### **Power Fluctuation**

- step power

- differences in the instantaneous power between consecutive cycles

- Inductive noise L•di/dt (voltage glitch induced at power/ground buses) ⇒ timing & logic errors

ESSES 2003 2003/7/22 (Jihong Kim)

43

#### **Step-power Aware Compilation**

- Programs spend most of the execution time in loops

- Optimizing compilers (for VLIWs) perform software pipelining to shorten the execution time of loops

- The traditional power-unaware software pipelining can be modified so that the <u>power fluctuation is</u> reduced

- Quite effective in reducing the power fluctuation

- The compiler can fully control the usage of all the FUs in a VLIW processor

ESSES 2003 2003/7/22 (Jihong Kim)

### VLIW machine model & power model

- MIPS-like integer pipeline, UltraSPARC-like FPU pipeline

- 8-issue VLIW model

- 1 integer ALU, 2 load/store unit, 1 integer MPY/DIV

- 2 FP ALU, 2 FP MPY/DIV

- 16-issue VLIW model: # of each FU is doubled

- Use instruction-level power model

- · ignore inter-instruction effect

- The proposed algorithm can be easily extended to work with more accurate power model

- does not depend on a particular power model

ESSES 2003 2003/7/22 (Jihong Kim)

45

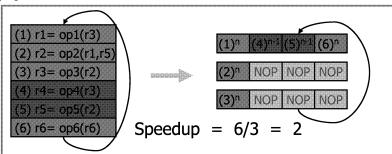

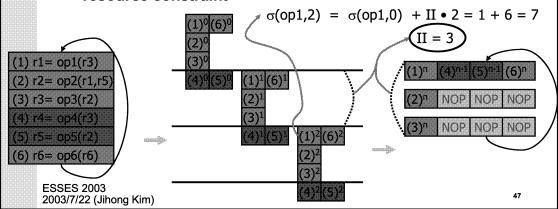

#### Software pipelining

- Aggressive fine-grained loop scheduling technique

- For VLIW processors (e.g., Intel IA-64, TI C6x, ...)

- Essentially, equivalent to retiming technique used in VLSI synthesis

- Overlaps the execution of multiple iterations in a pipelined fashion

Modulo scheduling is one of the scheduling algorithms for implementing software pipelining

ESSES 2003 2003/7/22 (Jihong Kim)

- II: the length of an iteration of parallelized loop body

- σ(op,i): execution cycle when the instance of operation op in iteration i is begin to execute

- Periodicity constraint : σ(op,i) = σ(op,0) + II i

- Goal : find the minimum II and a corresponding schedule  $\sigma(op,0)$  for each v subject to dependence constraint and resource constraint

#### Power-aware modulo scheduling

Our goal

Given the II (found by traditional MS algorithm), find the schedule such that the <u>power</u> consumption distribution is as **flat** as possible

No performance loss; no additional energy consumption

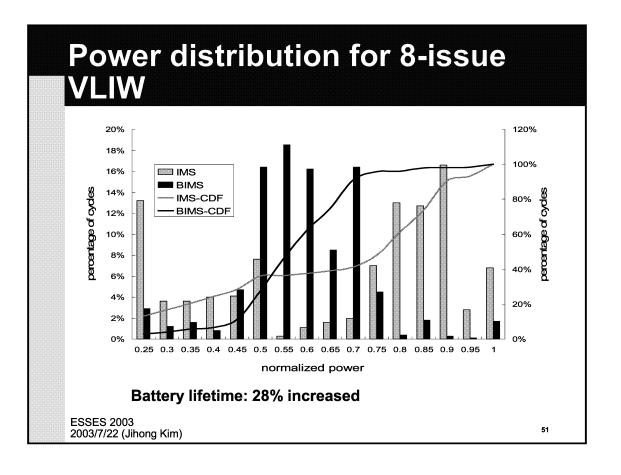

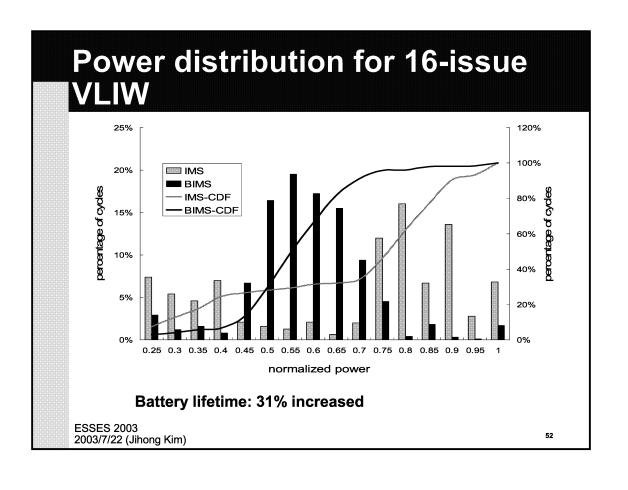

#### **Experiment setting**

- Base algorithm

- Iterative Modulo Scheduling (IMS) [Rau, MICRO'94]

- Outperforms most of other MS algorithms

- Our power-aware algorithm : Balanced IMS (BIMS)

- Battery lifetime model [Pedram, DAC'99]

- SPEC95 FP benchmark programs

- SPARC-based VLIW testbed [Moon, MICRO'97]

- 8 & 16-issue VLIW

#### Conclusion

- Quite effective in reducing the power fluctuation

- The compiler can fully control the usage of all the FU in a VLIW processor

- Battery lifetime increases significantly

- 29% for 8-issue VLIW

- 31% for 16-issue VLIW

ESSES 2003 2003/7/22 (Jihong Kim)

53

#### References

- D. Shin and J. Kim, "Operation Rearrangement for Low Power VLIW Instruction Fetch", Proc of DATE, 2001

- H.-S. Yun and J. Kim, "Power-Aware Modulo Scheduling for High-Performance VLIW Processors", Proc of ISLPED, 2001

ESSES 2003 2003/7/22 (Jihong Kim)

#### Roadmap

- ✓ Low-power systems 101

- √ Low-power binary encoding

- ✓ Power-aware compiler techniques

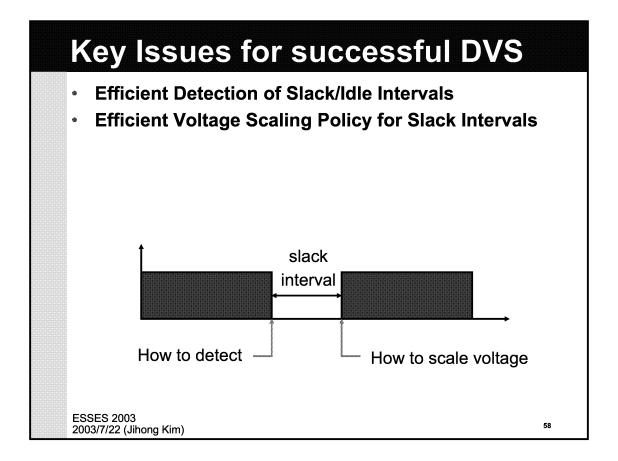

- Dynamic voltage scaling techniques

- intraDVS

- interDVS

- Low-power convolution

ESSES 2003 2003/7/22 (Jihong Kim)

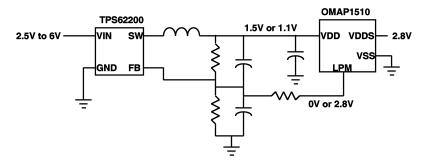

### **Commercial DVS Processors**

- Transmeta Crusoe

- AMD K2+ (PowerNow Technology)

- Intel SpeedStep

- XScale

ESSES 2003 2003/7/22 (Jihong Kim)

59

### **Voltage Scaling Processors**

|               | C                                | Commercial                     |                         | F                    | Academic                                                     |

|---------------|----------------------------------|--------------------------------|-------------------------|----------------------|--------------------------------------------------------------|

| Processors    | Transmeta<br>Crusoe<br>(LongRun) | AMD<br>Mobile K6<br>(PowerNow) | Intel<br>PXA250         | UC Berkely<br>(ARM8) | Ubicom<br>LART(StrongARM)                                    |

| Scaling Level | 200~700MHz<br>1.1~1.65V          | 192~588MHz<br>0.9~2.0V         | 100~400MHz<br>0.85~1.3V | 5~80MHz<br>1.2~3.8V  | 59~251MHz<br>0.79~1.65V                                      |

| Scaling Time  | 1.1 ↔ 1.65V<br>< 300μs           | 0.9 ↔2.0V<br>200μs             | Each step<br>500μs      | 1.2 ↔ 3.8V<br>520μs  | 59↔251MHz : 140μs<br>0.79→1.65V : 40μs<br>0.79←1.65V : 5.5ms |

| Scaling Power | ??                               | ??                             | ??                      | 130μJ                | 77                                                           |

ESSES 2003 2003/7/22 (Jihong Kim)

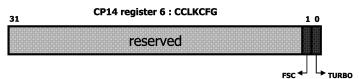

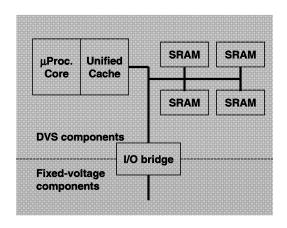

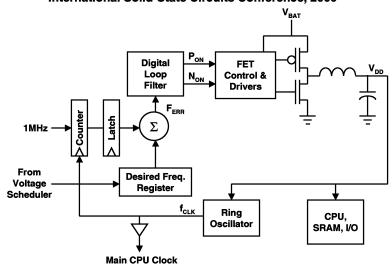

#### **DVS** in XScale

- Use Two Registers in PXA250 Xscale Core

- CCCR (Core Clock Configuration Register):

- Specify memory clock & core clock

- CCLKCFG (Core Clock Configuration) Register

- Set FCS (Frequency Change Sequence) bit to change the clock speed

Change if FCS bit = 1

ESSES 2003 2003/7/22 (Jihong Kim)

|   | 0x41300000 : CCCR 9 8 7 6 5 4 3 2 1 0 |       |      |        |      |       | D    |       |       |

|---|---------------------------------------|-------|------|--------|------|-------|------|-------|-------|

|   |                                       |       | res  | served |      |       | N M  |       |       |

| L | M                                     |       |      |        |      | V     |      |       |       |

|   | 171                                   | 2     | 2    |        | 3    | 4     | 1    |       | 3     |

| 1 | 1                                     | 99.5  | .85V |        |      | 199.1 | 1.0V | 298.6 | 1.1V  |

| 2 | 1                                     | 118.0 |      |        |      | 235.9 |      | 353.9 | 4 2)/ |

| 3 | 1                                     | 132.7 | 1.0V |        |      | 265.4 | 1.1V | 398.9 | 1.3V  |

| 4 | 1                                     | 147.5 |      |        |      | 294.9 |      |       |       |

| 5 | 1                                     | 165.9 |      |        |      | 331.8 | 1.3V |       |       |

| 1 | 2                                     | 199.1 |      | 298.6  | 1.1V | 398.1 | 1.3V |       |       |

| 2 | 2                                     | 235.9 |      |        |      |       |      |       |       |

| 3 | 2                                     | 265.4 | 1.1V |        |      |       |      |       |       |

| 4 | 2                                     | 294.9 |      |        |      |       |      |       |       |

| 5 | 2                                     | 331.9 | 1.3V |        |      |       |      |       |       |

#### Ex) DVS on PAX250

```

#include <machine/pmu.h>

#include <machine/cp14.h>

void Main(void)

int i, bb, cc, j;

int thread_args[3] = {0, 1, 2};

for ( k = 1 ; k < 13 ; k++ ) {

f (k = 1; k < 13; k++ ) {

change_clock_speed(k);

bb = get_os_time();

for (i = 0; i < 10000; i++ ) j = 10;

cc = get_os_time();

printf("%d : %d \n", k, cc - bb);</pre>

change_clock_speed(int speed)

11

12

13

14

15

cccr_val = settings[speed];

cccr_val = settings[speed];

switch (speed) {

case 6 : clkcfg_val = 3; break;

case 8 : clkcfg_val = 3; break;

case 10 : clkcfg_val = 3; break;

default : clkcfg_val = 2; break;

16

17

18

19

20

21

22

23

memcpy(0x40000000+0x1300000, &cccr_val, 4);

CP14_WRTIE_CCLKCFG(clkcfg_val);

}

24

25

26

27

28

int

get_os_time()

int ostime;

29

30

31

memcpy(&ostime, 0x40000000+0xa00010, 4);

return(ostime);

```

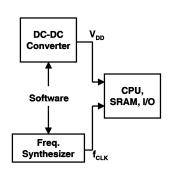

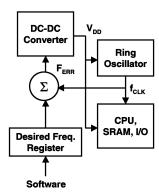

**DVS Outline**

**ESSES 2003**

2003/7/22 (Jihong Kim)

- DVS for Non-Real Time Systems

- DVS for Real-Time Systems

- · Intra-task DVS design techniques

- Inter-task DVS design techniques

- DVS-aware algorithm development

ESSES 2003 2003/7/22 (Jihong Kim)

64

#### **Non Real-Time Jobs**

- Non Real-Time Jobs

- No timing constraints

- Non-periodic execution

- Unknown WCET

It is hard to predict the future workload!!

ESSES 2003 2003/7/22 (Jihong Kim)

6

#### **DVS for Non-Real-Time Jobs**

- Usually based on Interval Scheduler

- PAST, FLAT

- LONG\_SHORT, AGED\_AVERAGE

- CYCLE, PATTERN, PEAK

ESSES 2003 2003/7/22 (Jihong Kim)

# **Major Issues**

#### How can we predict the future?

- Based on long term history:

Hard to adapt quickly for the changed workload

- Based on short term history:

Too many clock/voltage changes

ESSES 2003 2003/7/22 (Jihong Kim)

67

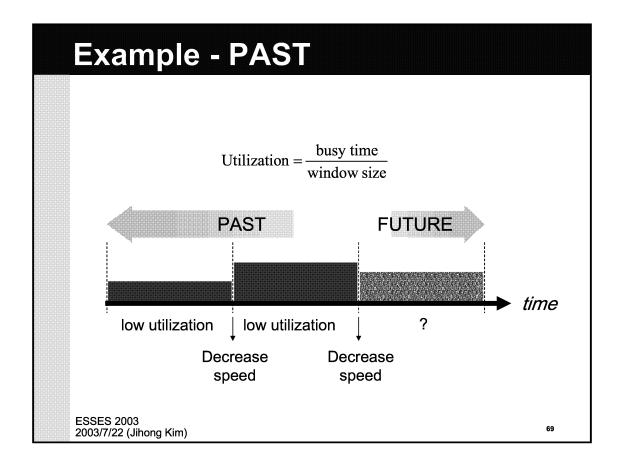

#### **PAST**

- Looking a fixed window into the past

- Assume the next window will be like the previous one

- If the past window was

- mostly busy  $\Rightarrow$  increase speed

- mostly idle ⇒ decrease speed

ESSES 2003 2003/7/22 (Jihong Kim)

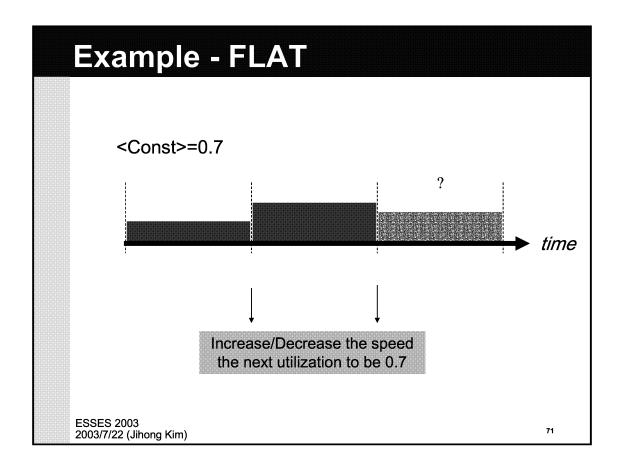

#### **FLAT**

- Try to smooth speed to a global average

- Make the utilization of next window to be <const>

- Set speed fast enough to complete the predicted new work being pushed into the coming window

#### LONG-SHORT

- Look up the last 12 windows

- Short-term past: 3 most recent windows

- Long-term past : the remaining windows

- Prediction

- the utilization of next window will be a weighted average of these 12 windows' utilizations

ESSES 2003 2003/7/22 (Jihong Kim)

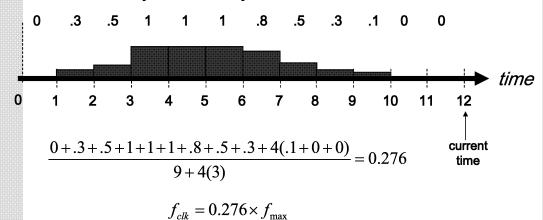

# **Example – LONG-SHORT**

utilization = # cycles of busy interval / window size

ESSES 2003 2003/7/22 (Jihong Kim)

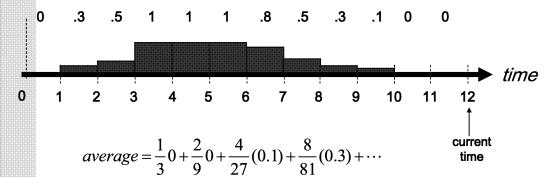

#### **AGED-AVERAGE**

- Employs an exponential-smoothing method

- Prediction

- The utilization of next window will be a weighted average of all previous windows' utilization

- geometrically reduces the weight

ESSES 2003 2003/7/22 (Jihong Kim)

# **Example – AGED\_AVERAGE**

utilization = # cycles of busy interval / window size

$$f_{clk} = average \times f_{max}$$

ESSES 2003 2003/7/22 (Jihong Kim)

75

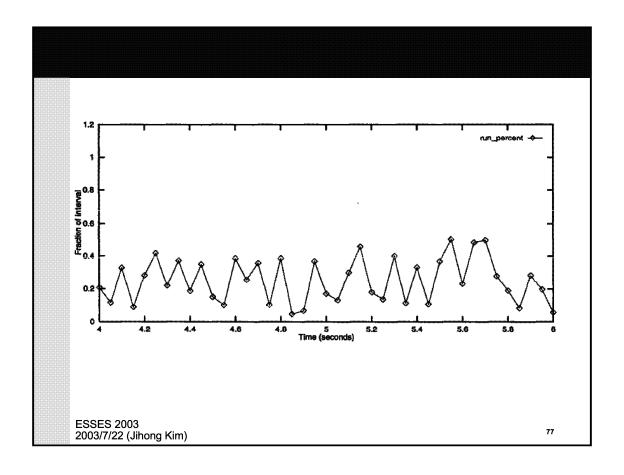

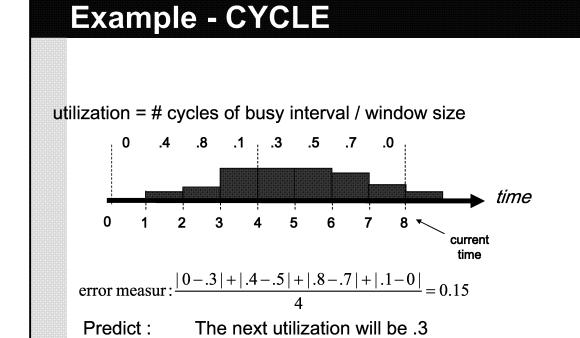

#### **CYCLE**

- Prediction

- Examine the last 16 windows

- Does there exist a cyclic of length X?

- If so, predict by extending this cycle

- Otherwise, use the FLAT algorithm

ESSES 2003 2003/7/22 (Jihong Kim)

78

ESSES 2003 2003/7/22 (Jihong Kim)

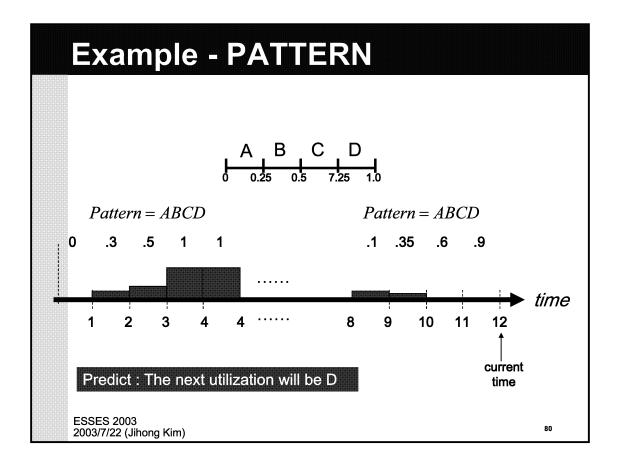

#### **PATTERN**

- Generalized version of CYCLE

- Prediction

- Convert the n-most recent windows' utilization into a pattern in alphabet {A, B, C, D}.

- Find a same pattern in the past

- Set the speed based on the prejudication

ESSES 2003 2003/7/22 (Jihong Kim)

#### **DVS Outline**

- DVS for Non-Real Time Systems

- DVS for Real-Time Systems

- Intra-task DVS design techniques

- Inter-task DVS design techniques

- DVS-aware algorithm development

ESSES 2003 2003/7/22 (Jihong Kim)

81

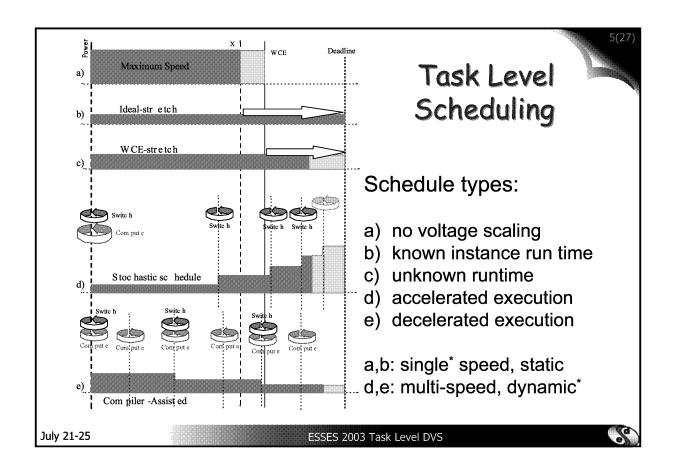

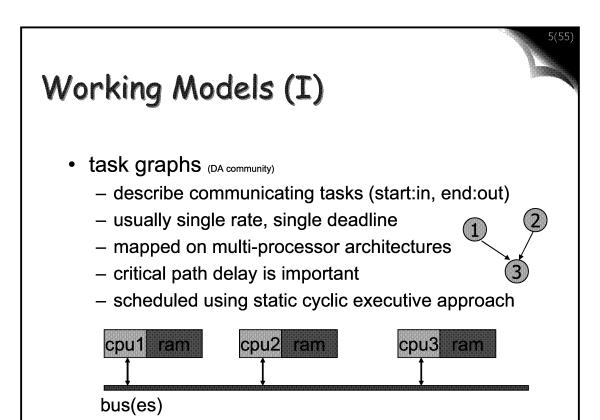

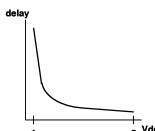

# Two Types of DVS Algorithms

- Inter-task DVS algorithms

- Determine the supply voltage and clock speed on task-by-task basis

- Intra-task DVS algorithms

- Determine the supply voltage and clock speed within a single task boundary

ESSES 2003 2003/7/22 (Jihong Kim)

#### **Related Work: Inter-task DVS**

- Inter-Task Voltage Scheduling for Hard Real-Time Systems [Yao95, Hong98, Okuma99, Shin99, Lee99].

- Problem: Given a set of tasks, how to assign the proper speed to each task dynamically while guaranteeing all their deadlines.

- Task-by-task Speed Assignment

- The slack time due to a task used by following tasks, not by the current one.

- Practical Limitations

- Requires OS modifications

- Cannot be applied to a single-task environment

- Can be ineffective in a multi-task environment

ESSES 2003 2003/7/22 (Jihong Kim)

83

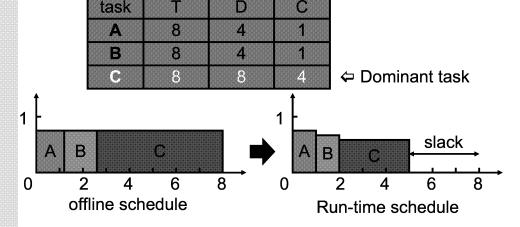

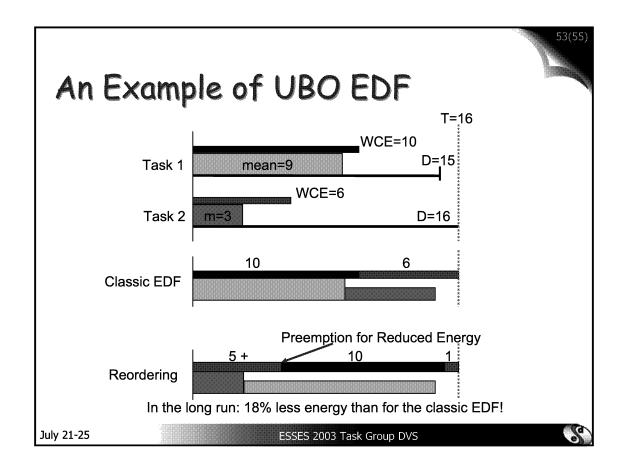

# An Example of Ineffective Inter

- A dominant task (C)

- Exploits small slack times from other tasks.

- Cannot use its own.

ESSES 2003 2003/7/22 (Jihong Kim)

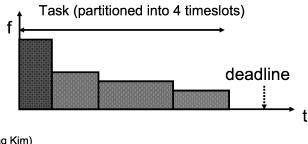

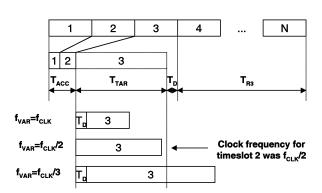

# Related Work: Intra-task DVS

- Run-time voltage hopping [Lee00]

- Each task is partitioned into N timeslots.

- Frequency and voltage determined for each timeslot.

- Voltage scheduling embedded in application programs.

- Can be applied to conventional non-DVS OS.

- No systematic guideline

- Manual selection of scaling points

- Too much burden for average programmers

ESSES 2003 2003/7/22 (Jihong Kim)

85

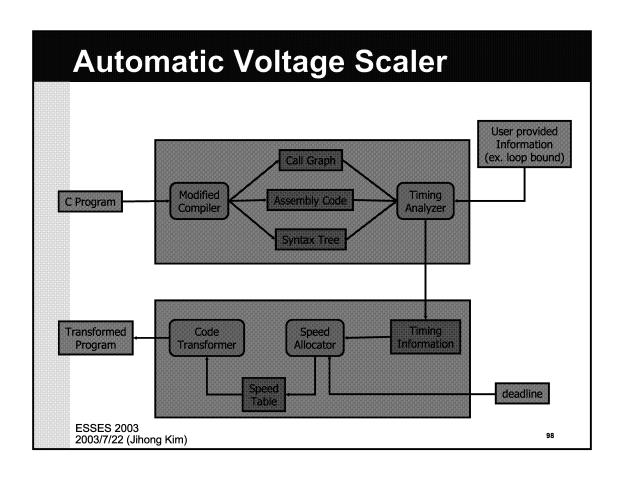

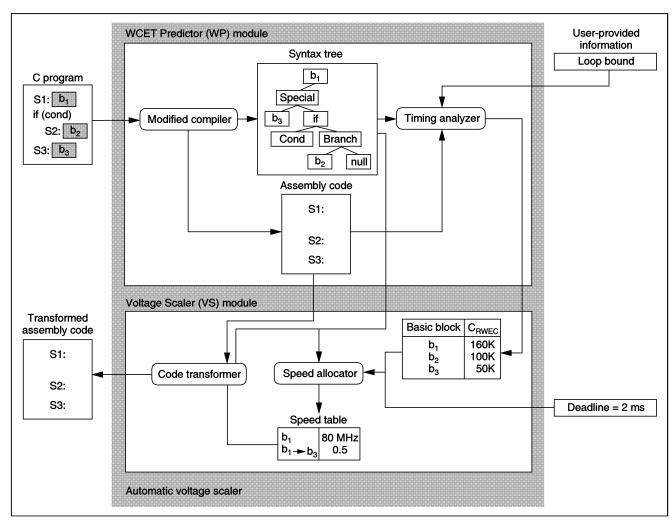

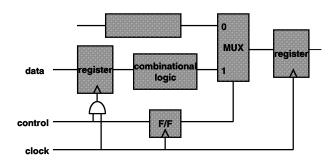

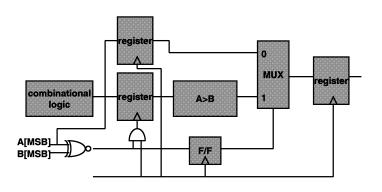

#### **Overview**

- A novel intra-task voltage scheduling framework based on a static timing analysis of RT programs.

- The clock speed is adjusted in a task by embedded codes.

- Fully exploits all slack times coming from execution time variations within a single task

- No OS modification

- Applicable to a single-task environment.

- Provides a systematic methodology for developing DVSaware programs

- ⇒Automatic Voltage Scaler Tool

ESSES 2003 2003/7/22 (Jihong Kim)

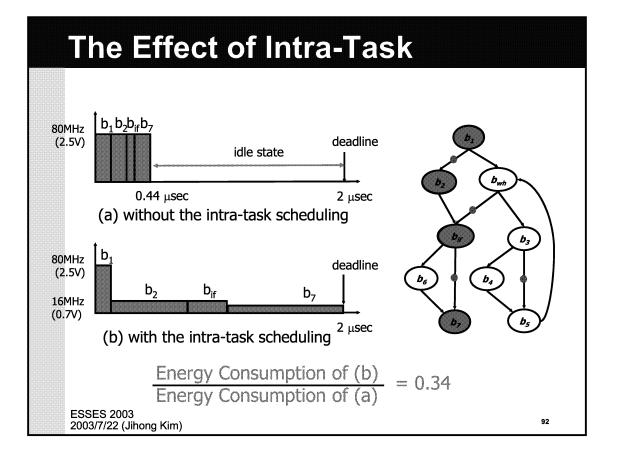

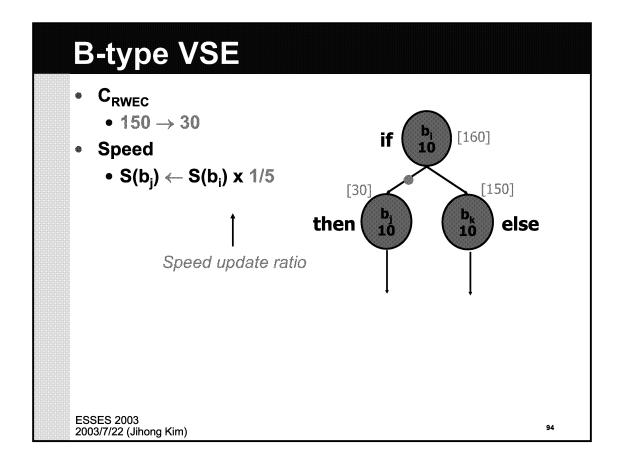

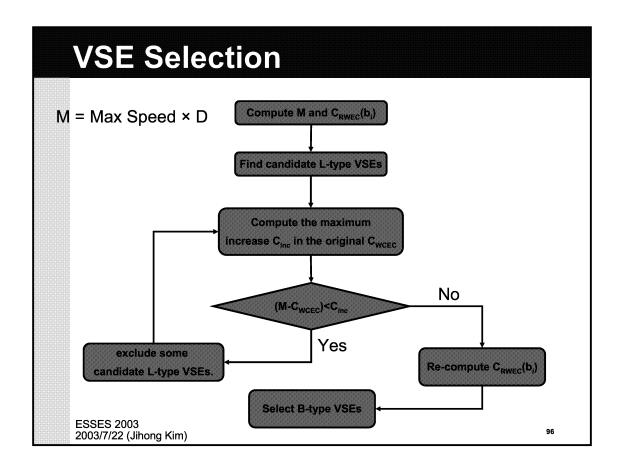

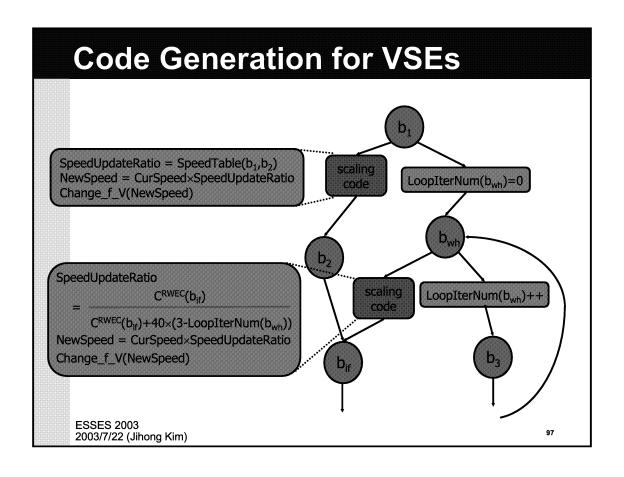

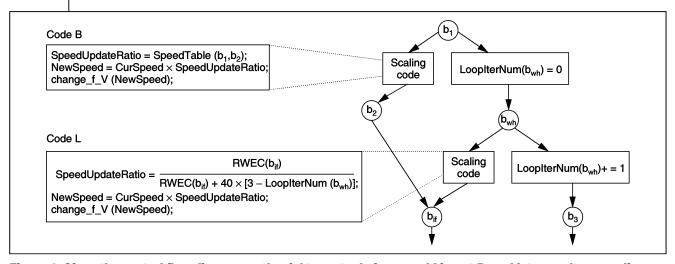

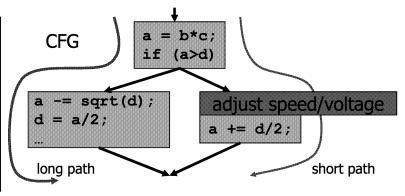

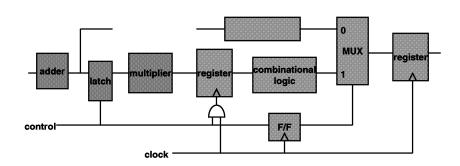

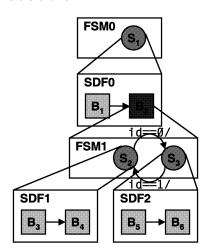

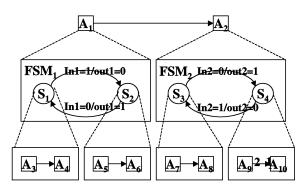

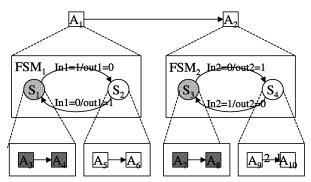

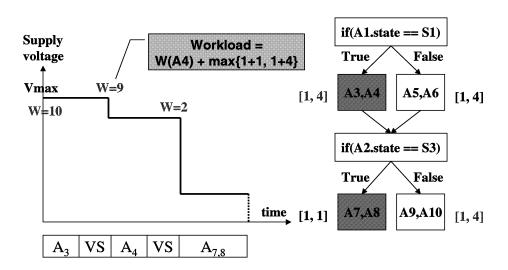

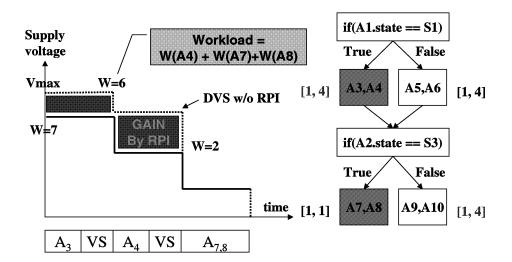

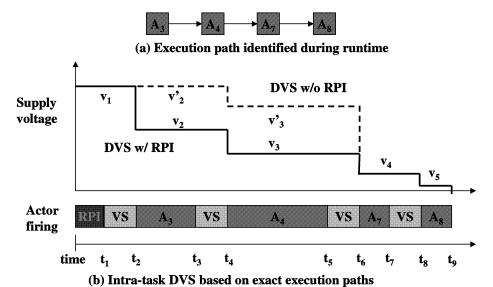

# Speed Assignment Algorithm

- Branching edges are candidate for speed changes :

- Branches: The execution control follows the shorter path at if-then-else node. => B-type VSEs

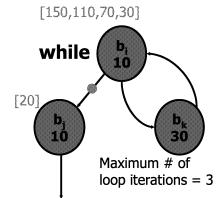

- Loops: The execution control exits a loop after it iterates by the smaller number of times than the maximum iteration number. => L-type VSEs

ESSES 2003 2003/7/22 (Jihong Kim)

# L-type VSE

When the actual loop iterations measured at run time is 2

- $60 \rightarrow 20$

- Speed

- $S(b_i) \leftarrow S(b_i) \times 1/3$

Speed update ratio

The transition overhead is considered to determine a new speed.

ESSES 2003 2003/7/22 (Jihong Kim)

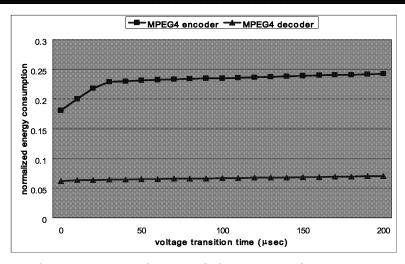

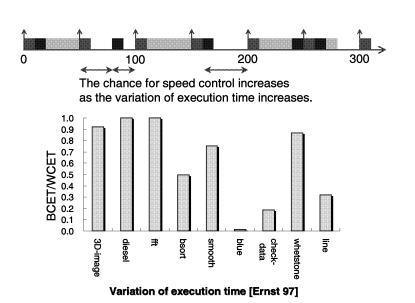

#### **Simulation Results**

- Less than 25% and 7% of the original program

- There is a large difference between WCET and ACET of the MPEG-4 decoder

ESSES 2003 2003/7/22 (Jihong Kim)

99

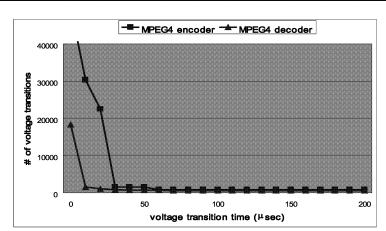

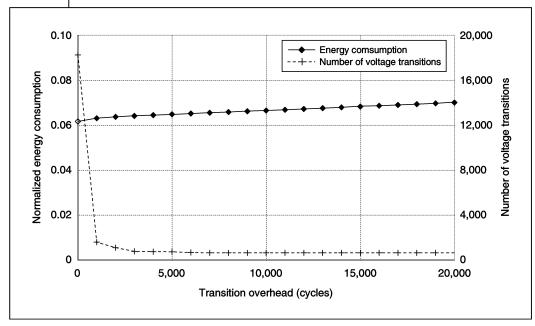

#### **Simulation Results**

- How many times voltage scaling code were executed

- When  $C_{VTO}$  <  $30\mu sec$  in MPEG-4 encoder, the number of voltage transitions decreases sharply, and energy consumption does not increase rapidly.

- How many copies of voltage scaling code?

- 20 VSEs are inserted when  $C_{VTO} > 50 \mu sec.$

**ESSES 2003**

2003/7/22 (Jihong Kim)

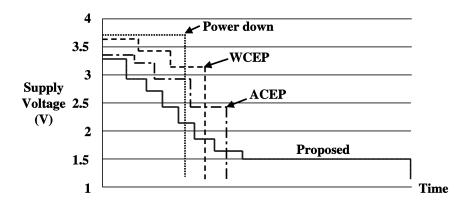

#### A Profile-Based Intra-Task

- IntraVS algorithm based on average-case execution information

- Average-case execution paths (ACEPs) are the most frequently executed paths

- More effective than the original intraVS algorithm

- The timing constraints of a hard real-time program is still satisfied, even if the ACEPs are used for voltage scaling decisions.

ESSES 2003 2003/7/22 (Jihong Kim)

#### **RAEP-based IntraVS**

- Motivations

- To make the common case more energyefficient

- If we use one of hot paths as a reference path for intraVS, the speed change graph for the hot paths will be a near flat curve with little changes in clock speed.

- Even for the paths that are not the hot paths, they are more energy-efficient because they can start with a lower clock speed that RWEP-based IntraVS.

- RAEP is the best representative of the hot paths.

ESSES 2003 2003/7/22 (Jihong Kim)

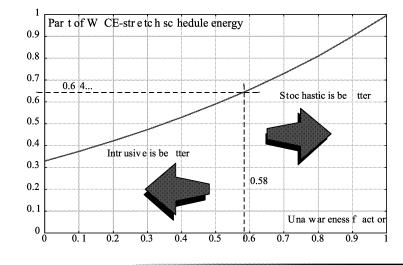

Slack Factor = (deadline-WCET)/deadline

ESSES 2003 2003/7/22 (Jihong Kim)

107

#### Conclusion

- Presented a novel intra-task DVS algorithm using static timing analysis on RWECs

- Provides a framework for automatic DVS-aware lowpower program generation

- The RAEP-based IntraVS algorithm exploits the fact that the average-case execution paths are more likely to be followed at run time than the WCEP.

- Demonstrated the effectiveness of the approach using MPEG-4 encoder/decoder programs

ESSES 2003 2003/7/22 (Jihong Kim)

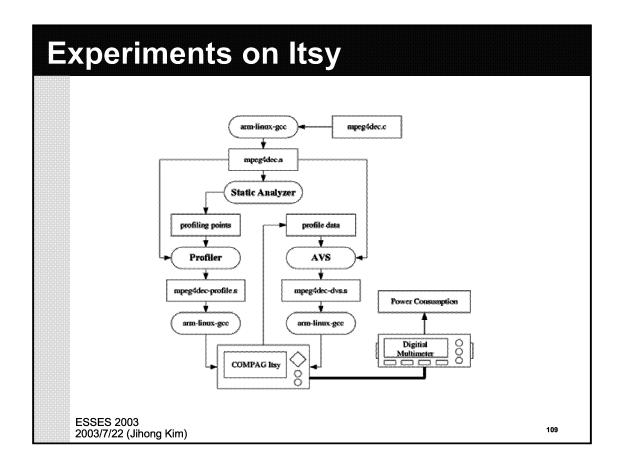

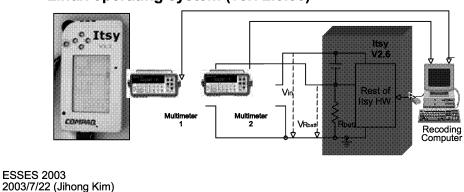

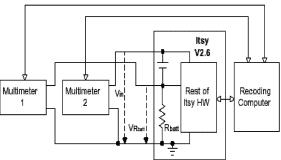

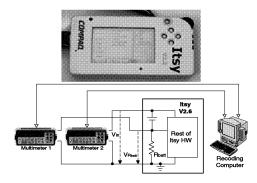

# **Experimental Environment**

- Itsy Pocket Computer V2.6

- CPU: Intel StrongARM SA1110

- Frequency scaling: 11 levels (59.0 MHz ~ 206.4 MHz)

- Voltage scaling: 30 levels (1.00 V ~ 2.00 V)

- Default setting: 1.55 V/206.4 MHz

- Linux operating system (ver. 2.0.30)

# **Experimental Results**

DVS EXPERIMENTS ON ITSY.

|                      |          | MPEG-4 Decoder |            | MPEG-4 encoder |            |

|----------------------|----------|----------------|------------|----------------|------------|

| Factors              |          | DVS-aware      | normal     | DVS-aware      | normal     |

| Energy (mJ)          |          | 0.11           | 0.22(0.18) | 0.28           | 0.81(0.62) |

| Normalized Energy    |          | 0.51(0.62)     | 1          | 0.35(0.46)     | 1          |

| Execution Time (sec) |          | 1.18           | 0.46       | 5.34           | 1.54       |

| WCET (sec)           |          | 3.2            |            | 21.0           |            |

| Selected<br>VSEs     | B-VSE    | 2              |            | 1              |            |

|                      | L-VSE    | 1              |            | 2              |            |

| Management<br>Code   | Function | 2              |            | 3              |            |

|                      | Loop     | 5              |            | 8              |            |

MANAGEMENT CODE OVERHEAD.

| Management Code | Code number in Fig. 7 | Number of assembly instructions |

|-----------------|-----------------------|---------------------------------|

| Loop Enter      | code 1 and 2          | 30                              |

| Loop Header     | code 3                | 16                              |

| Loop Exit       | code 4                | 16                              |

| Punction Enter  | code 5                | 14                              |

| Function Return | code 6                | 11                              |

| B-type VSE      | code B                | ≈ 200                           |

| L-type VSE      | code L                | ≈ 200                           |

ESSES 2003 2003/7/22 (Jihong Kim)

111

# **Experimental Results**

ESSES 2003 2003/7/22 (Jihong Kim)

#### Roadmap

- ✓ Low-power systems 101

- √ Low-power binary encoding

- ✓ Power-aware compiler techniques

- Dynamic voltage scaling techniques

- √ intraDVS

- interDVS

- Low-power convolution

ESSES 2003 2003/7/22 (Jihong Kim)

113

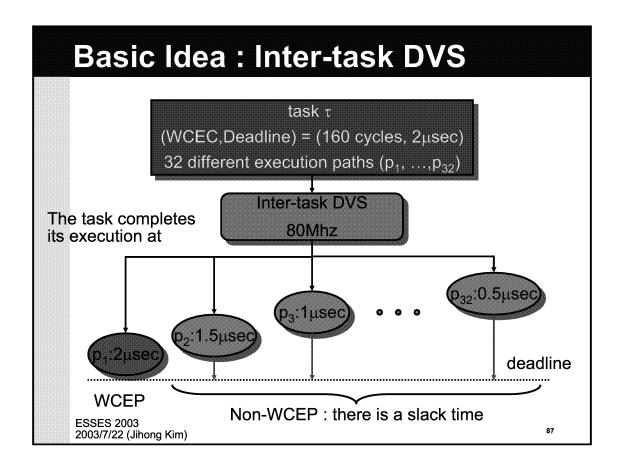

#### Introduction

- Inter-task DVS algorithms

- Determine the supply voltage and clock speed on task-by-task basis

- Inter-task DVS

- Is similar to that of imprecise computation in conventional real-time systems

- -Imprecise computation

- Use the slack time to increase the values of results

- · While guaranteeing the feasible schedule of tasks

- Dynamic voltage scaling

- Use the slack time to lower the voltage/clock speed

- · While guaranteeing the feasible schedule of tasks

ESSES 2003 2003/7/22 (Jihong Kim)

#### **Preliminaries**

- Computing model

- Non-real-time

- -tasks have no timing constraints

- Real-Time

- -Timing constraints

- -Periodic and(or) aperiodic tasks

- -Scheduling policy: EDF, RM, and etc.

- Different DVS algorithms are necessary depending on different computing models.

ESSES 2003 2003/7/22 (Jihong Kim)

115

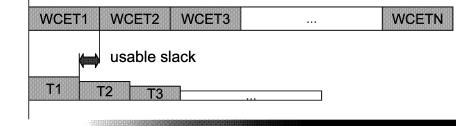

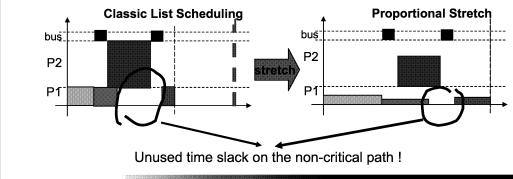

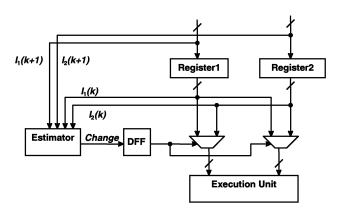

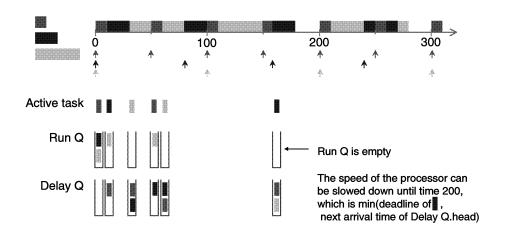

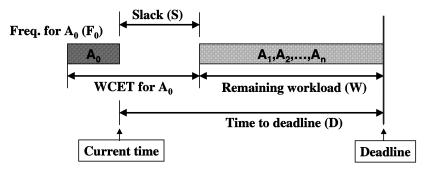

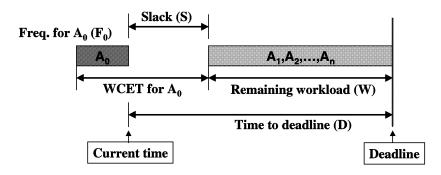

#### Inter-Task DVS

- "Run-Calculate-Assign-Run" strategy for the supply voltage determination

- Running the current task

- Calculating the maximum allowable execution time for the next task

- -WCET plus slack time

- Assigning the supply voltage for the next task

- Running the next task

ESSES 2003 2003/7/22 (Jihong Kim)

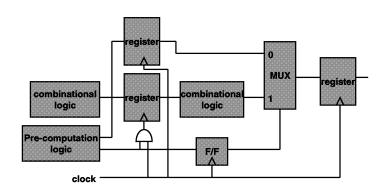

#### **Generic Inter-DVS Algorithms**

- Consist of two parts

- Slack estimation

- -Identify as much slack times as possible

- -Slack times

- Static slack times

- Extra times available for the next task that can be identified statically

- Dynamic slack times

- Ones caused from run-time variations of the task executions

- Slack distribution

- Adjust the speed so that the resultant speed schedule is as flat as possible

ESSES 2003 2003/7/22 (Jihong Kim)

117

# Static and Dynamic Approaches

- Off-line (Static) voltage scheduling approaches

- The execution times are assumed to be known a priori

- There are several optimal solutions for EDF, RM, and etc.

- On-line (Dynamic) voltage scheduling approaches

- The execution times are assumed to be not known

- There cannot be an optimal solution

ESSES 2003 2003/7/22 (Jihong Kim)

#### **Slack Estimation Methods**

|            | Voltage Scaling Methods           | Scaling<br>Decision |  |

|------------|-----------------------------------|---------------------|--|

| IntraDVS - | (1) Path-based method             | Off-line            |  |

| Illuadvs   | (2) Stochastic method             |                     |  |

|            | (3) Maximum constant speed        |                     |  |

| TtoDVC     | (4) Stretching to NTA             | On-line             |  |

| InterDVS   | (5) Priority-based slack-stealing |                     |  |

|            | (6) Utilization updating          |                     |  |

**ESSES 2003** 2003/7/22 (Jihong Kim)

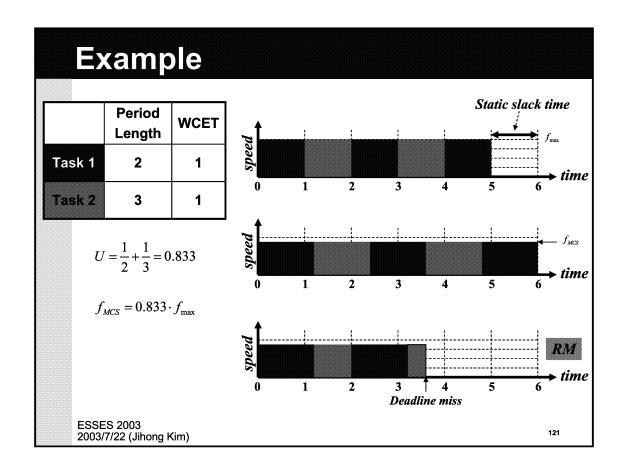

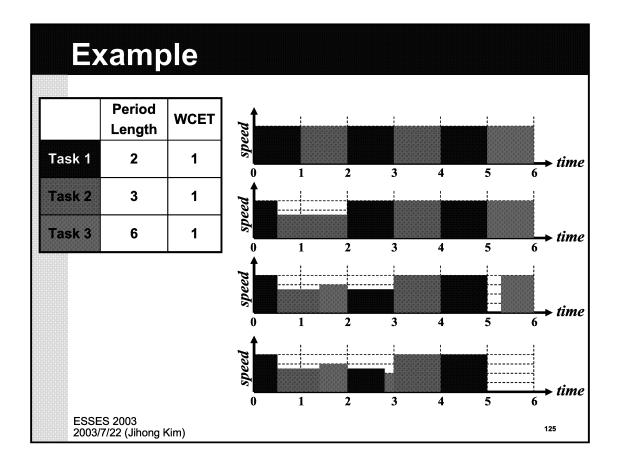

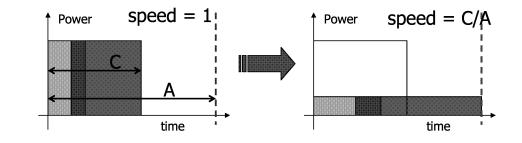

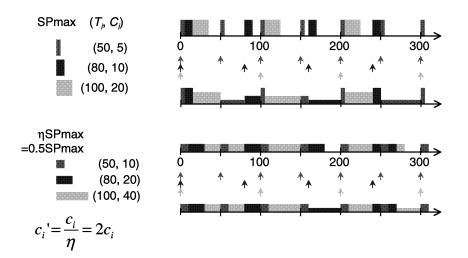

# **Maximum Constant Speed**

- The lowest possible clock speed that guarantees the feasible schedule of a task set

- **EDF** scheduling

- -If the worst case processor utilization U of a given task set is lower than 1.0 under the maximum speed  $f_{\rm max}$  , the task set can be scheduled with a new maximum speed

$$U = \sum_{i=1}^{n} \frac{c_i}{p_i}$$

$f_{MSC} = U \cdot f_{max}$  Rate Monotonic scheduling

Maximum constant speed

$$L_{i}(t) = \frac{\sum_{j=1}^{i} \left[ \frac{t}{T_{j}} \right] C_{j}}{t} \qquad f_{MCS} = f_{\max} \times \max_{i} \{ L_{i}(t) \mid 1 < i \le n, 0 < t < d_{i} \}$$

**ESSES 2003** 2003/7/22 (Jihong Kim)

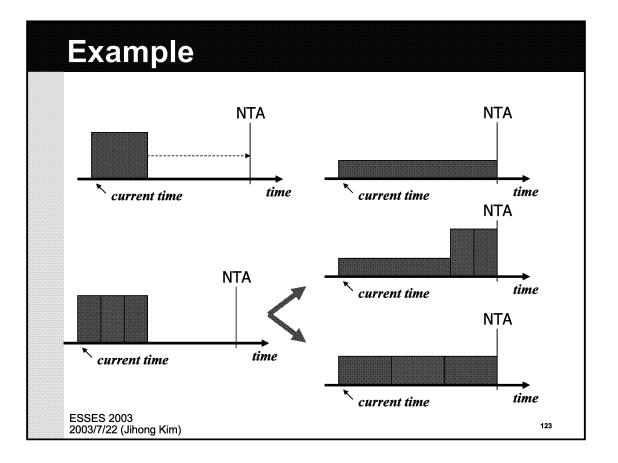

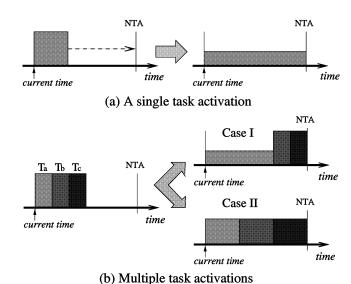

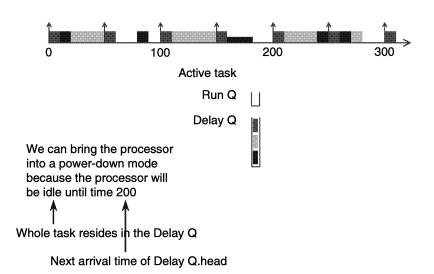

# Stretching to NTA

- Even though a given task set is scheduled with the maximum constant speed, since the actual execution times of tasks are usually much less than their WCETs, the tasks usually have dynamic slack times

- For the task  $\tau$  which is scheduled at time t

- If the next task is later than  $t + WCET(\tau)$

- We can slow down the execution of  $\tau$  so that its execution completes exactly at this next task arrival time (NTA)

#### **Priority-Based Slack Stealing**

- Exploits basic properties of priority-driven scheduling such as EDF and RM

- When a higher-priority task completes its execution earlier than its WCET, the following lower-priority tasks can use the slack time from the completed higher-priority task

- Advantage

- Most task instances in a hyper-period may have chances to utilize dynamic slack times

- Because most task executions complete earlier than WCETs

- Therefore, many task instances can be scheduled with lowered voltages and speeds

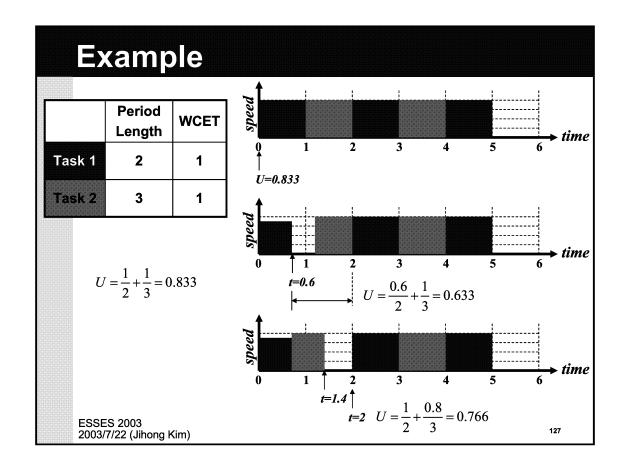

# **Utilization Updating**

- The actual processor utilization during run time is usually lower than the worst case processor utilization

- This method is to estimate the required processor performance at the current scheduling point

- By recalculating the expected worst case processor utilization

- Using the actual execution times of completed task instances

# **Slack Distribution Method**

- Greedy approach

- All the slack times are given to the next activated task

- Most inter-task DVS algorithms have adopted it

- Clearly, this approach is not an optimal solution, but is widely used because of its simplicity

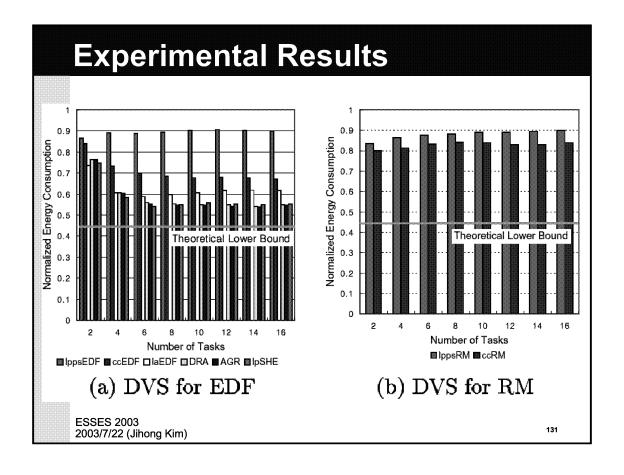

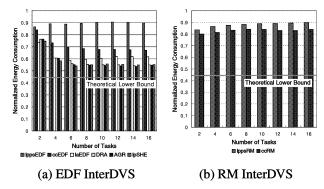

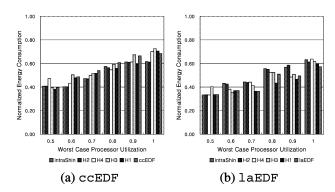

# **Existing Inter-Task DVS Algorithms**

| Category          | Scheduling Policy | DVS Policy  | <b>Used Method</b> |

|-------------------|-------------------|-------------|--------------------|

| Inter-task<br>DVS |                   | IppsEDF     | (3)+(4)            |

|                   |                   | ccEDF       | (6)                |

|                   | EDF               | laEDF       | (6)*               |

|                   | EDF               | DRA         | (3)+(4)+(5)        |

|                   |                   | AGR         | (4)*+(5)           |

|                   |                   | IpSEH       | (3)+(4)+(5)*       |

|                   | RM                | IppsRM      | (3)+(4)            |

|                   | KIT               | ccRM        | (4)*               |

| Intra-task        | Path-based method | intraShin   | (1)                |

| DVS               | Stochastic method | intraGruian | (2)                |

ESSES 2003 2003/7/22 (Jihong Kim)

129

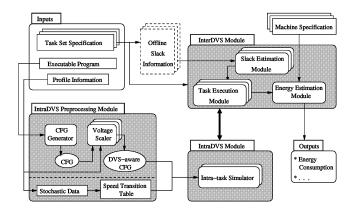

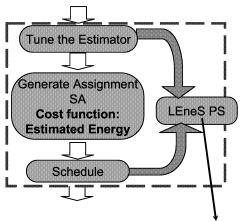

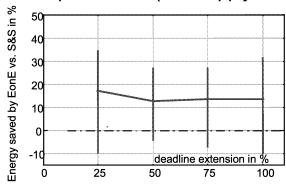

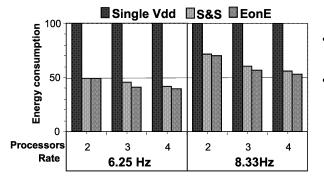

#### SimDVS: A Unified DVS Evaluation Environment Task Set Generator Machine specification InterDVS Module **Inputs** Off-line Slack Estimation Task Set Specification Slack Module information **Executable Program** Profile Information Energy Estimation Task Execution Module Module **IntraDVS Preprocessing Module** Voltage Scaler CFG IntraDVS Module Outputs DVS-aware CFG \* Energy consumption CFG Generator Speed Transition Stochastic Data **ESSES 2003** 130 2003/7/22 (Jihong Kim)

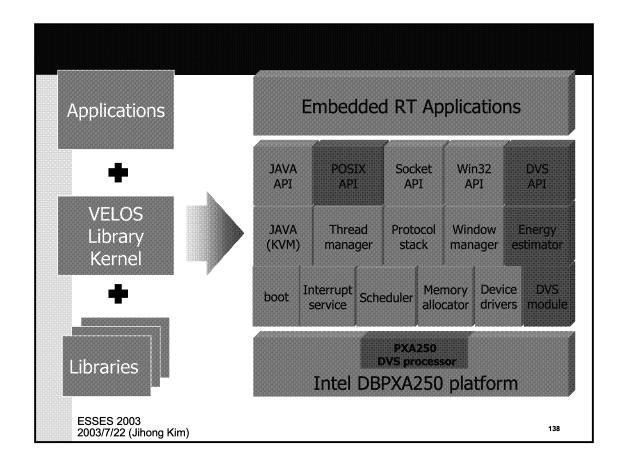

# Performance Evaluation DVS Algorithms for Hard Real-Time Systems Using DEW

#### **DEW - DVS Evaluation Workbench**

- XScale-based DVS evaluation environment

- Pros

- Allows to monitor real system behaviors under DVS

- Cons

- Slower than software simulation

- Because DEW runs actual applications

- Less flexible for experimental studies

- Because DEW represents a single machine specification

VELOS

Embedded RT Applications

VELOS

Embedded RTos

PXA250

DVS processor

Intel DBPXA250

ESSES 2003 2003/7/22 (Jihong Kim)

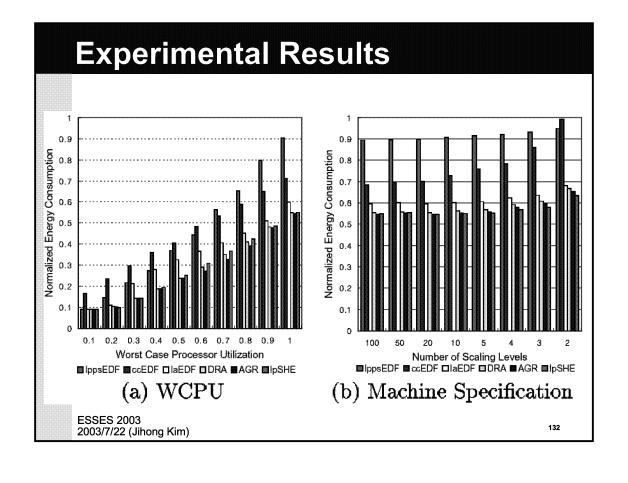

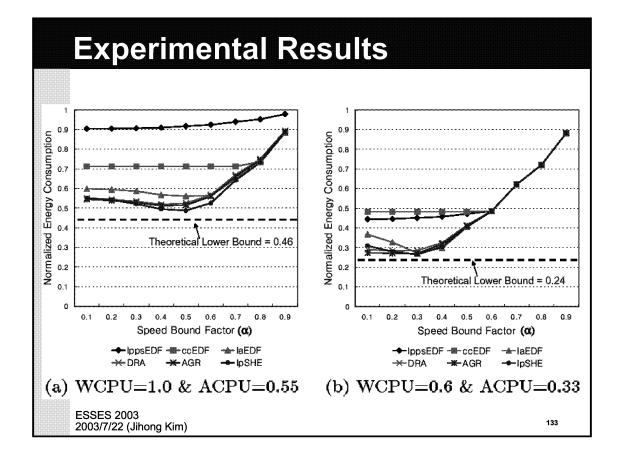

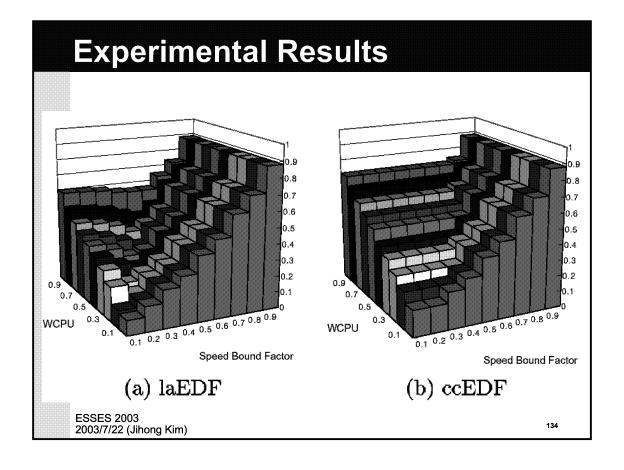

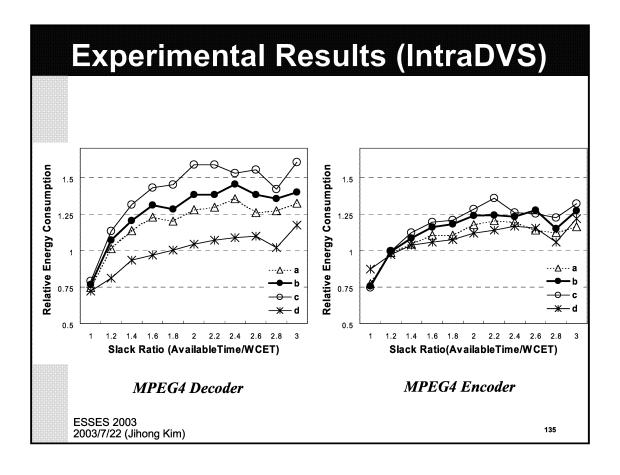

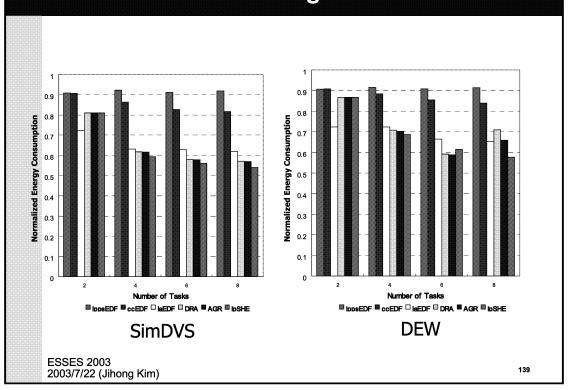

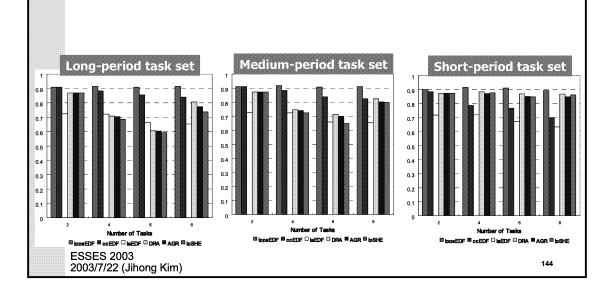

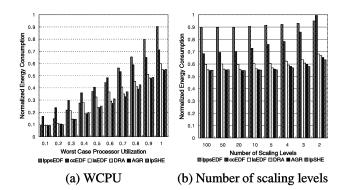

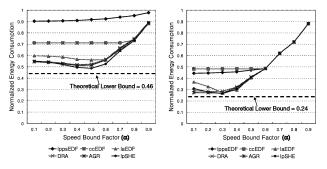

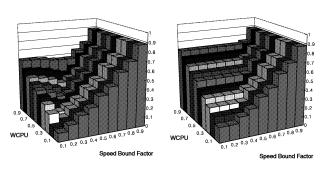

## **Evaluation Results Using SimDVS and DEW**

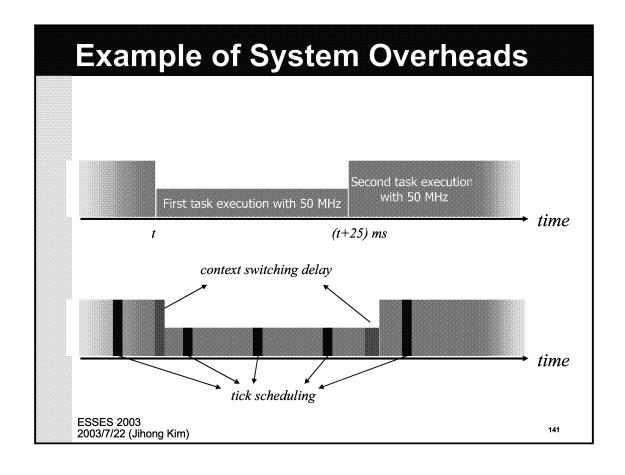

# **Sources of Differences**

- Impacts of

- System overhead

- Basic : context switching overhead and tick scheduler overhead

- DVS : slack computation and clock/voltage scaling

- System timing resolution

- Simulator : continuous time model

- Real system : discrete time model

- Memory behavior

- Changes in cache and memory access behavior

- Data/Instruction fetch latency

ESSES 2003 2003/7/22 (Jihong Kim)

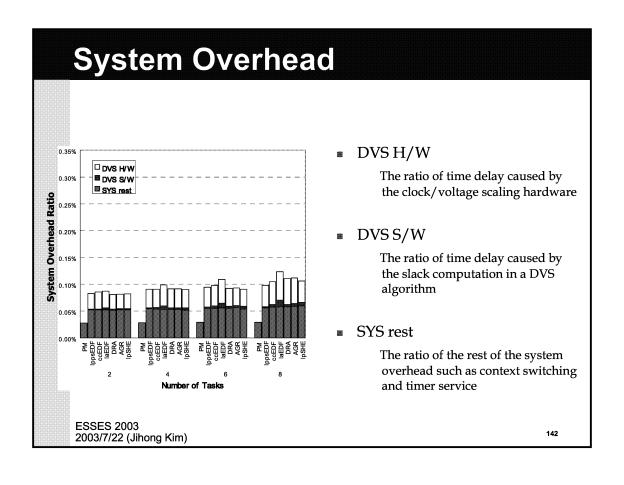

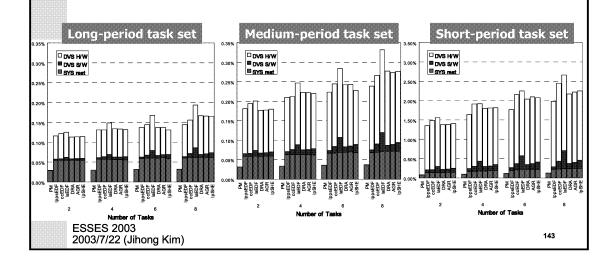

# **System Overhead Variations**

- The system overhead increases very quickly as the task execution frequency increases

- In particular, DVS parts increase quickly

# **Energy Efficiency Variations**

In DRA, AGR, and IpSHE, the increased system overhead (due to the increased execution frequency) significantly affect the energy efficiency

# **Changes in Memory System**

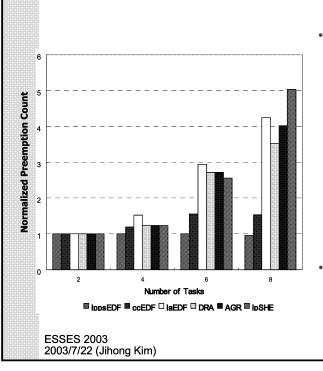

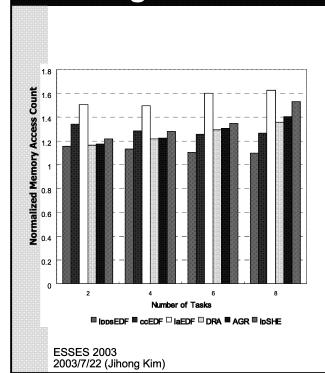

- Under a DVS-enabled RTOS, Task's execution time increases due to the lowered clock speed

- Desirable for reducing energy consumption

- But, it can introduce negative side effects as well

- An increase in the number of task preemptions which increases the number of memory accesses

- In aggressive algorithms, the number of preemptions increases more rapidly than the others

145

# **Changes in Memory System**

- PXA250

- Performance Monitoring Unit

- 32-way set-associative cache of Inst/Data cache

- Each application

- 16-KB program code

- The increases in memory accesses can be attributed to two sources

- The increase in the number of preemptions

- The increase in memory accesses from the algorithm itself

## References

- Transmeta Corporation. Crusoe Processor. http://www.transmeta.com, June 2000.

- AMD Corporation. PowerNow! Technology. http://www.amd.com, December 2000.

- Intel Corporation. Intel XScale Technology. http://developer.intel.com/ design/ intelxscale/, November 2001.

- I. Hong, G. Qu, M. Potkonjak, and M. B. Srivastava. Synthesis Techniques for Low-Power Hard Real-Time Systems on Variable Voltage Processor. In Proceedings of the IEEE Real-Time Systems Symposium, pages 178-187, December 1998.

- Y. Shin, K. Choi, and T. Sakurai. Power Optimization of Real-Time Embedded Systems on Variable Speed Processors. In Proceedings of the International Conference on Computer-Aided Design, pages 365-368, November 2000.

- H. Aydin, R. Melhem, D. Mosse, and P. M. Alvarez. Dynamic and Aggressive Scheduling Techniques for Power-Aware Real-Time Systems. In Proceedings of IEEE Real-Time Systems Symposium, December 2001.

ESSES 2003 2003/7/22 (Jihong Kim)

147

# References

- P. Pillai and K. G. Shin. Real-Time Dynamic Voltage Scaling for Low-Power Embedded Operating Systems. In Proceedings of 18th ACM Symposium on Operating Systems Principles (SOSP'01), October 2001.

- D. Shin, J. Kim, and S. Lee. Intra-Task Voltage Scheduling for Low-Energy Hard Real-Time Applications. IEEE Design and Test of Computers, 18(2):20-30, March 2001.

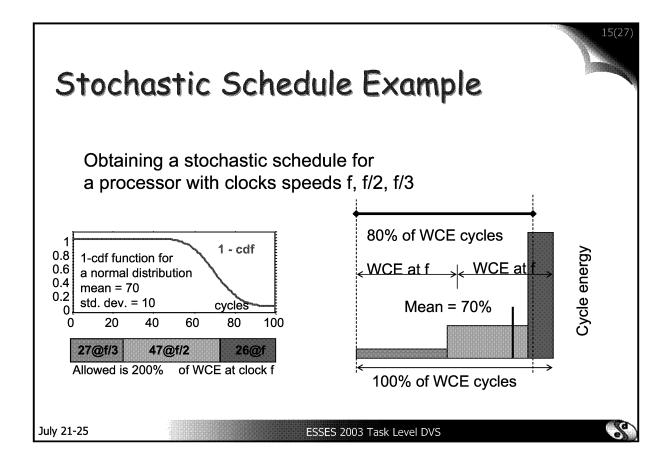

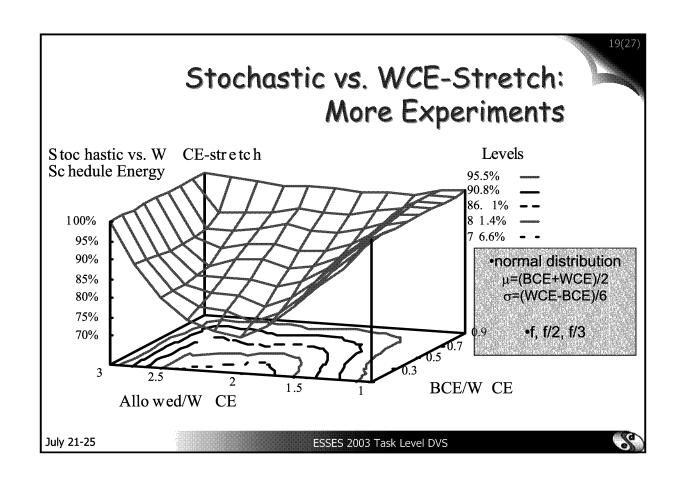

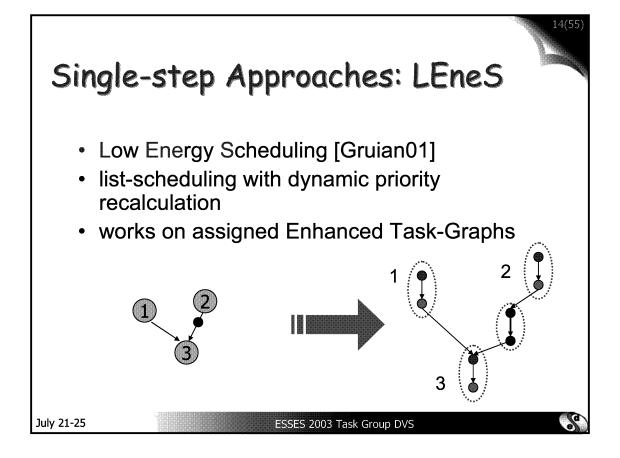

- F. Gruian. Hard Real-Time Scheduling Using Stochastic Data and DVS Processors. In Proceedings of the International Symposium on Low Power Electronics and Design, pages 46-51, August 2001.

- W. Kim, J. Kim, and S. L. Min. A Dynamic Voltage Scaling Algorithm for Dynamic-Priority Hard Real-Time Systems Using Slack Time Analysis. To appear in Proceedings of Design, Automation and Test in Europe (DATE'02), March 2002.

ESSES 2003 2003/7/22 (Jihong Kim)

# References

- D. Grunwald, P. Levis, and K. I. Farkas. Policies for Dynamic Clock Scheduling. In Proceedings of the 4th Symposium on Operating Systems Design and Implementation, pages 73-86, October 2000.

- S. Lee and T. Sakurai. Run-time Voltage Hopping for Lowpower Real-Time Systems. In Proceedings of the 37th Design Automation Conference, pages 806-809, June 2000.

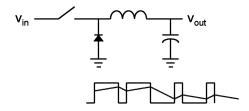

- T. Burd and R. Brodersen. Design Issues for Dynamic voltage scaling. In Proceedings of the International Symposium on Low Power Electronics and Design, pages 9-14, July 2000.

- D. Burger and T. M. Austin. The SimpleScalar Tool Set, version 2.0. Technical Report 1342, University of Wisconsin-Madison, CS Department, June 1997.

- F. Yao, A. Demers, and A. Shenker. A Scheduling Model for Reduced CPU Energy. In Proceedings of the IEEE Foundations of Computer Science, pages 374-382, 1995.

ESSES 2003 2003/7/22 (Jihong Kim)

149

# **DVS-Aware Algorithm Development**

ESSES 2003 2003/7/22 (Jihong Kim)

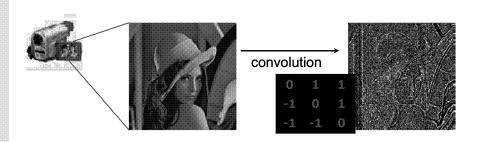

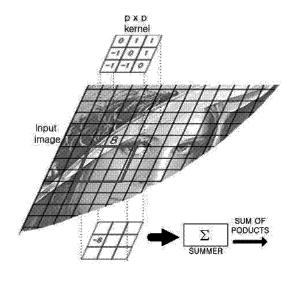

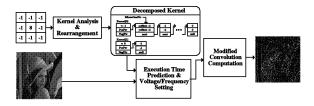

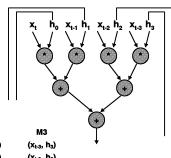

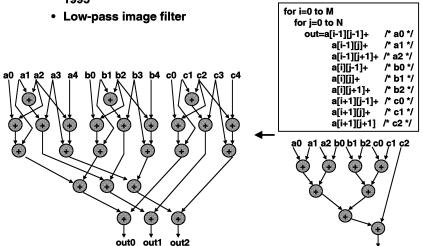

# **Image Convolution**

- One of the fundamental operations of image processing.

- DVS Unfriendly!!

ESSES 2003 2003/7/22 (Jihong Kim)

151

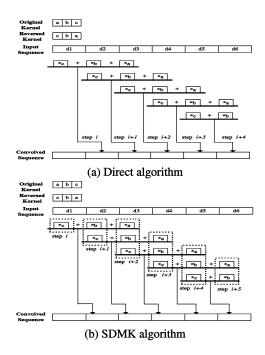

# **Direct Implementation:**

p² multiplications

p² additions for

each convolved

element.

No Workload Variations!

ESSES 2003 2003/7/22 (Jihong Kim)

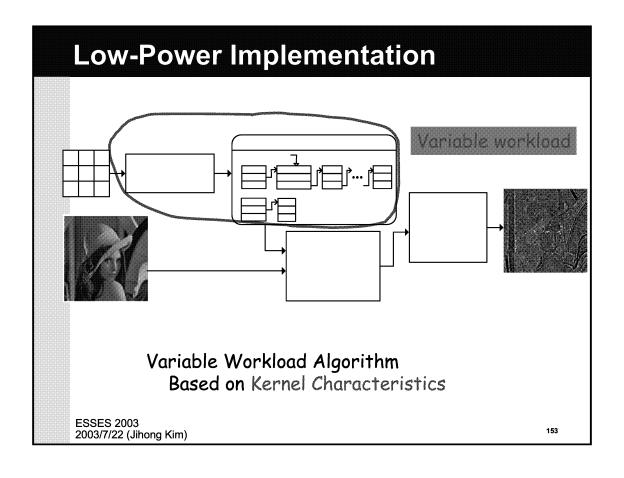

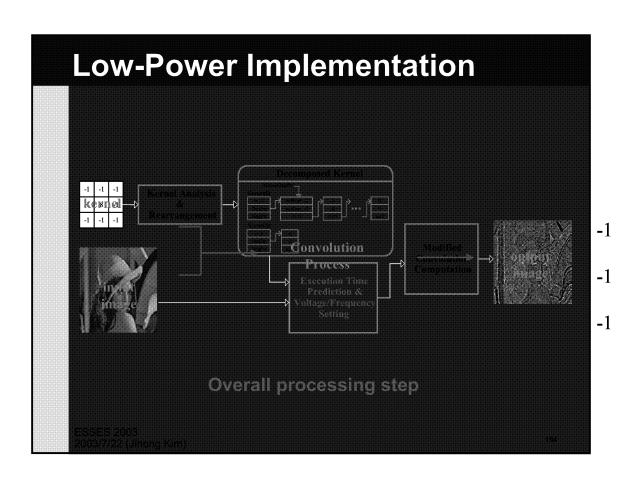

# **Kernel Analysis and Rearrangement**

- Property 1. For most kernels, the number of distinct kernel elements is small.

- Property 2. 0, 1 and -1 are used frequently.

- Property 3. Many kernel elements have the same absolute values.

ESSES 2003 2003/7/22 (Jihong Kim)

155

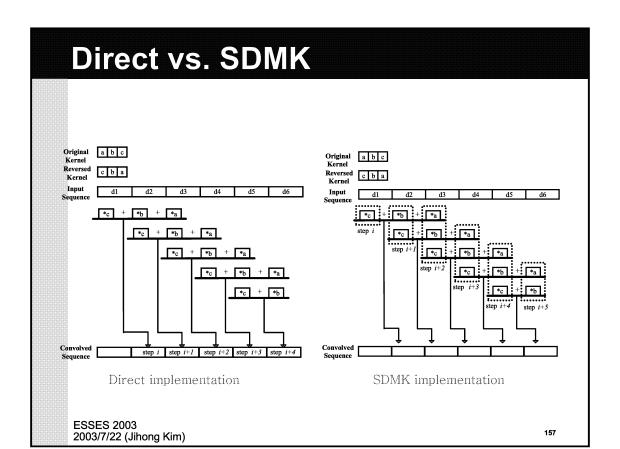

# **Modified Convolution Algorithm: SDMK**

- For 1 or –1, no multiplication.

- For 0, no addition & no multiplication.

- For the same absolute values, a single multiplication.

| 0  | 1  | 1 |

|----|----|---|

| -1 | 0  | 1 |

| -1 | -1 | 0 |

|                  | Direct            | SDMK              |

|------------------|-------------------|-------------------|

| Number of        | 9 additions &     | 6 additions &     |

| Operations/pixel | 9 multiplications | 0 multiplications |

ESSES 2003 2003/7/22 (Jihong Kim)

# **Exec Time Prediction & Speed Setting**

- By a static method

- Based on the number of required arithmetic operations

- By a dynamic-method

- Based on actual measurements of execution times

- In the direct algorithm, by pre-constructed speed table

ESSES 2003 2003/7/22 (Jihong Kim)

# **Experimental Environments**

- Itsy Pocket Computer V2.6

- CPU: Intel StrongARM 1110

- Frequency scaling: 11 levels (59.0 MHz ~ 226.4 MHz)

- Voltage scaling: 30 levels (1.00 V ~ 2.00 V)

- Linux operating system (ver. 2.0.30)

ESSES 2003 2003/7/22 (Jihong Kim)

159

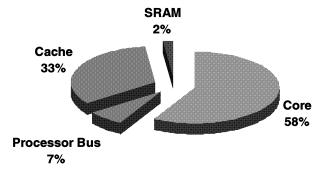

# Results (Energy Dissipation)

Average 67.6% energy saving in the core processor, and 62.8% in the whole Itsy system.

ESSES 2003 2003/7/22 (Jihong Kim)

# Results (Execution Time)

There is no performance degradation over the direct approach.

ESSES 2003 2003/7/22 (Jihong Kim)

161

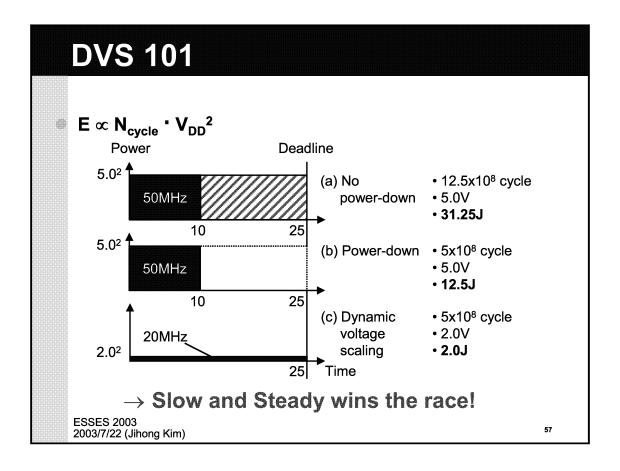

# **Conclusions**

- Presented a low-power implementation of image convolution algorithm for variable voltage processors.

- The energy efficiency of the proposed implementation comes from:

- Smaller N<sub>cycle</sub>

- Lower V<sub>dd</sub>

- $E \propto N_{cycle} \cdot V_{DD}^2$

- Fewer memory references

- i.e., less energy consumed in non-CPU components

ESSES 2003 2003/7/22 (Jihong Kim)

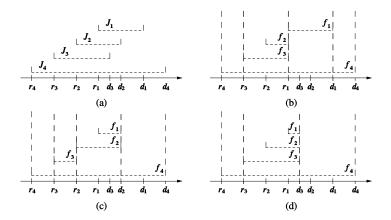

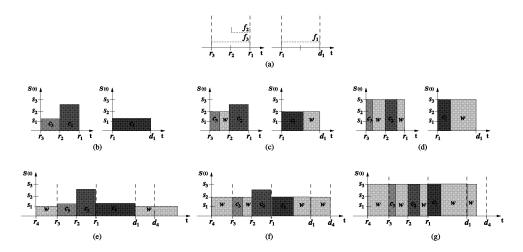

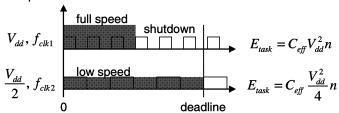

# **Energy-Optimal Off-Line Voltage Scheduling**

# Off-Line Volt. Sched. Problem

- Voltage schedule (speed schedule): S(t)

- the processor speed as a function of time

- The energy consumption under S(t) is given by

E(S) = ∫<sub>interval</sub> P(S(t)) dt

- -P is a convex function from speed to power

- Given N jobs J<sub>1</sub>, J<sub>2</sub>, ..., J<sub>N</sub> where

- r<sub>i</sub>: the release time of J<sub>i</sub>

- d<sub>i</sub>: the deadline of J<sub>i</sub>

- c<sub>i</sub>: the workload (# of execution cycles) of J<sub>i</sub>

- assumed to be known a priori

- p<sub>i</sub>: the priority of J<sub>i</sub>

compute a feasible voltage schedule S(t) that minimizes E(S)

• S(t) is feasible iff S(t) gives  $J_i$  its workload  $c_i$  between  $r_i$  and  $d_i$  for all  $J_1, J_2, \ldots, J_N$

ESSES 2003 2003/7/22 (Jihong Kim)

# Existing Works for the Problem

- Note that the system model covers

- Fixed-priority (RM, DM) periodic/aperiodic task set

- EDF periodic/aperiodic task set

- $-p_i < p_i$  iff  $d_i < d_i$

- For EDF job sets (a special case), the problem can be solved in poly. time by Yao's algo.[FOCS'95]

- solution space = convex , obj. func. = convex

- For general job sets, the problem becomes much difficult

- main source of difficulty: feasibility condition

- Quan & Hu [TCAD'03]: exhaustive optimal algo.

- Yun & Kim [TECS'03]: NP-hardness & FPTAS

2003/7/22 (Jihong Kim)

165

## References

- Optimal algorithm for EDF job sets

- F. Yao, A. Demers, S. Shenker, "A Scheduling Model for Reduced CPU Energy", In Proc. Foundations of Computer Sciences (FOCS'95), 1995

- **Heuristic for FP job sets**

- G. Quan and X. Hu, "Energy Efficient Scheduling for Real-Time Systems On Variable Voltage Processor", In Proc. Design Automation Conference (DAC'01), 2001.

- Exhaustive optimal algorithm for FP job sets

- G. Quan and X. Hu, "Minimum Energy Fixed Priority Scheduling for Variable Voltage Processors", IEEE Transactions on Computer Aided Design and Systems, 2003.

- NP-hardness proof & FPTAS for FP job sets

- H.-S. Yun and J. Kim, "On Energy-Optimal Voltage Scheduling for Fixed-Priority Hard Real-Time Systems", ACM Transactions on Embedded Computing Systems, 2003.

**ESSES 2003** 2003/7/22 (Jihong Kim)

# A Profile-Based Energy-Efficient Intra-Task Voltage Scheduling Algorithm for Hard Real-Time Applications\*

Dongkun Shin

School of Computer Science and Engineering

Seoul National University

sdk@davinci.snu.ac.kr

Jihong Kim

School of Computer Science and Engineering

Seoul National University

iihong@davinci.snu.ac.kr

### **ABSTRACT**

Intra-task voltage scheduling (IntraVS), which adjusts the supply voltage within an individual task boundary, is an effective technique for developing low-power applications. In this paper, we propose a novel intra-task voltage scheduling algorithm for hard real-time applications based on average-case execution information. Unlike the original IntraVS algorithm where voltage scaling decisions are based on the worst-case execution cycles, the proposed algorithm improves the energy efficiency by controlling the execution speed based on average-case execution cycles while still meeting the real-time constraints. The experimental results using an MPEG-4 decoder program show that the proposed algorithm reduces the energy consumption by up to 34% over the original IntraVS algorithm.

### 1. INTRODUCTION

Since energy consumption E of CMOS circuits has a quadratic dependency on the supply voltage  $V_{DD}$ , lowering the supply voltage  $V_{DD}$  is the most effective way of reducing energy consumption. However, lowering the supply voltage also decreases the clock speed, since the CMOS circuit delay  $T_D$  is given by  $T_D \propto V_{DD}/(V_{DD} - V_T)^{\alpha}$  [6], where  $V_T$  is a threshold voltage, and  $\alpha$  is a velocity saturation index. This trade-off introduced various dynamic voltage scaling (DVS) techniques. DVS techniques change the clock speed and its corresponding supply voltage dynamically to the lowest possible level while meeting the task's performance constraint.

### 1.1 Dynamic Voltage Scaling

For hard real-time systems, there exist two DVS approaches depending on the scaling granularity. *Inter-task voltage scheduling* (InterVS) [9, 2, 8, 5] determines the supply voltage on task-bytask basis, while *intra-task voltage scheduling* (IntraVS) [4, 7] adjusts the supply voltage within an individual task boundary. Both approaches can guarantee the required performance constraints of real-time systems.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

*ISLPED'01*, August 6-7, 2001, Huntington Beach, California, USA. Copyright 2001 ACM 1-58113-371-5/01/0008 ...\$5.00.

Intra-task voltage scheduling [4, 7] has been proposed as a solution to overcome the limitations of inter-task voltage scheduling. IntraVS algorithms exploit all the slack time from run-time variations of different execution paths; there is no slack time when the scheduled program completes its execution, thus significantly improving energy efficiency. Furthermore, since IntraVS does not involve OS in adjusting the clock speed, it can be used with an existing OS without any modifications on a variable voltage processor.

We propose an energy-efficient IntraVS algorithm for hard realtime applications based on *average-case* execution information. Unlike the original IntraVS algorithm [7] where voltage scaling decisions are based on *worst-case execution cycles*, the proposed algorithm controls the execution speed based on the *average-case* execution paths (ACEPs), which are the most frequently executed paths. Since the proposed algorithm is optimized for the energy reduction in the ACEP(s), which are the most likely path(s) that will be executed at run time, the proposed algorithm is more effective than the original intraVS algorithm [7] in reducing the energy consumption. The novel aspect of the proposed algorithm is that the timing constraints of a hard real-time program is still satisfied, even if the ACEP(s) are used for voltage scaling decisions.

# 2. ORIGINAL INTRA-TASK VOLTAGE SCHEDULING ALGORITHM

For a hard real-time task, the goal of an intra-task voltage scheduling algorithm is to assign a proper clock speed to each basic block so that energy consumption is minimized while satisfying timing requirements. In this section, we briefly describe the original intra-task voltage scheduling algorithm [7] as a short introduction to intra-task voltage scheduling.

Throughout this paper, we assume the following about the target variable voltage processor: The processor provides a special instruction, change\_f\_V ( $f_{CLK}$ ), which changes the current clock frequency to  $f_{CLK}$  and adjusts the supply voltage to the corresponding voltage  $V_{DD}$ .  $f_{CLK}$  and  $V_{DD}$  can be set continuously within the operational range of the processor. When the processor changes the clock/voltage, there is a clock/voltage transition overhead. During clock/voltage transition, the processor stops running.

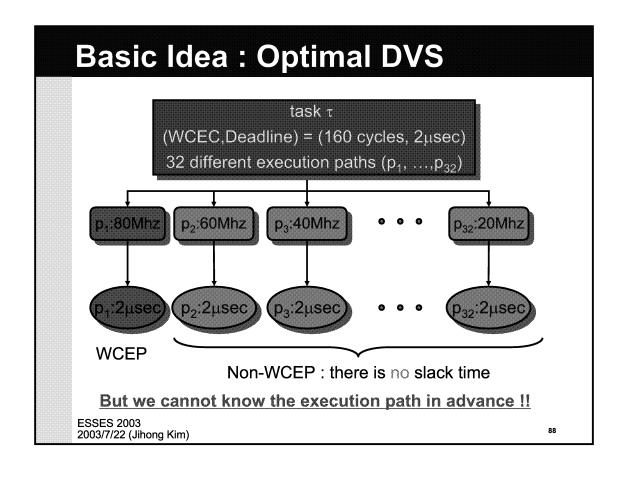

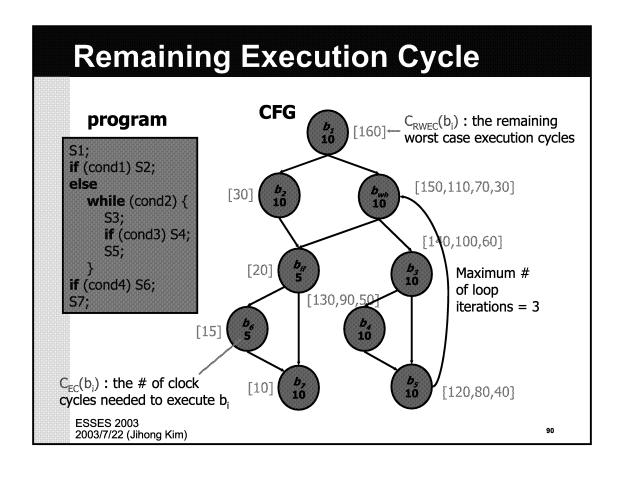

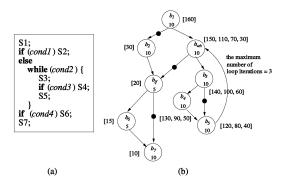

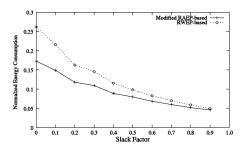

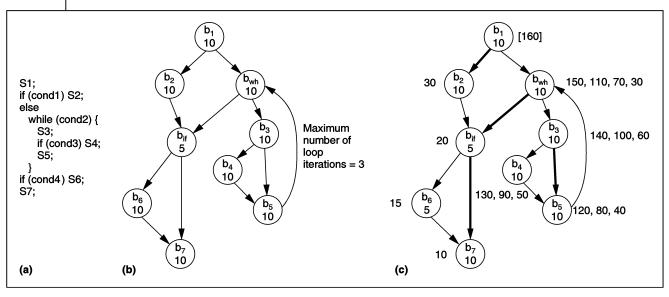

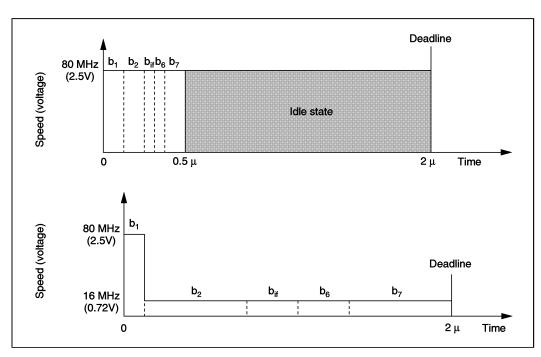

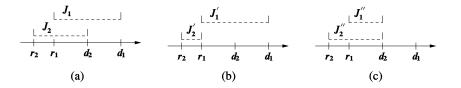

Consider a hard real-time program P with the deadline of 2  $\mu$ sec shown in Fig. 1(a). The CFG  $G_P$  of the program P is shown in Fig. 1(b). In  $G_P$ , each node represents a basic block of P and each edge indicates the control dependency between basic blocks. The number within each node indicates  $C_{EC}(b_i)$  which is the number of execution cycles of the corresponding basic block. The back edge from  $b_5$  to  $b_{wh}$  models the **while** loop of the program P.

Using a WCET analysis tool, we can find the path  $p_{worst} = (b_1, b_{wh}, b_3, b_4, b_5, b_{wh}, b_3, b_4, b_5, b_{wh}, b_{if}, b_6, b_7)$  as the worst case

<sup>\*</sup>This work is supported by the Ministry of Information & Communication of Korea (Support Project of University foundation research<'00> supervised by IITA).

execution path (WCEP) for the example program P, assuming that the maximum number of **while** loop iterations is set to 3 by user. The predicted execution cycles of  $p_{worst}$  is, therefore, 160 cycles, which is the worst case execution cycles (WCEC) of program P. If a target processor operates at the maximal 80-MHz clock frequency, the program P completes its execution in 2  $\mu$ sec, resulting in no slack time.

Figure 1: An example program; (a) an example real-time program P and (b) its CFG  $G_P$ .

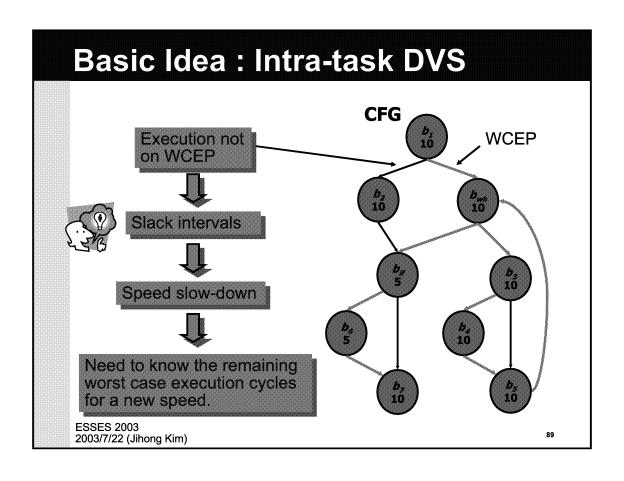

The key observation behind the IntraVS approach is that there are large execution time variations among different execution paths. For short execution paths, if we were able to identify them in the early phase of its execution, we can lower the clock speed substantially, thus saving a significant amount of energy consumption.

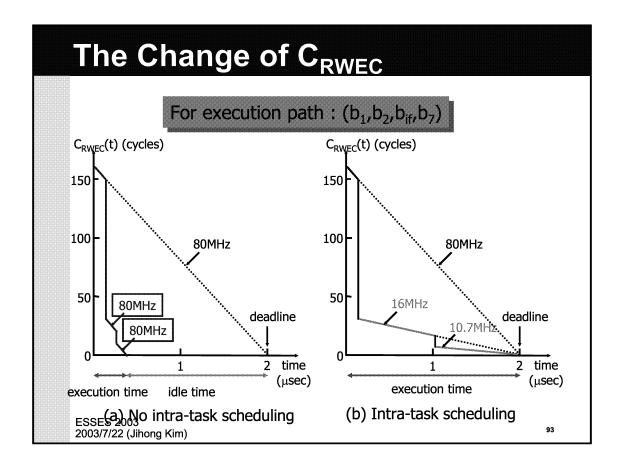

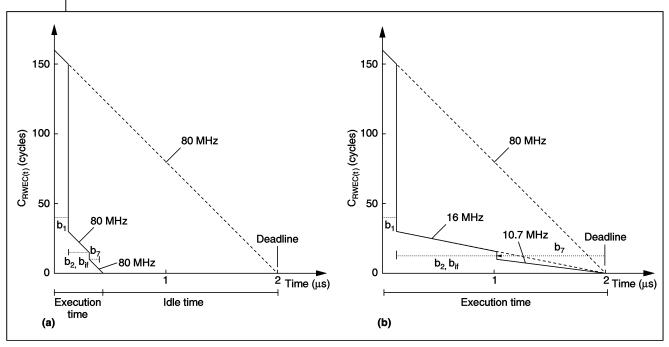

For the speed adjustment, intra-task voltage scheduling technique uses an adaptive approach with the help of a static program analysis technique on worst case execution times. Assume that  $C_{RWEC}(b_i)$  represents the remaining worst case execution cycles (RWEC) among all the execution paths that start from  $b_i$ . Using a modified WCET analysis tool, for each basic block  $b_i$ , we can compute  $C_{RWEC}(b_i)$  in *compile time*. In Fig. 1(b), the symbol [] contains the  $C_{RWEC}(b_i)$  values of each basic block. For the basic blocks related to the **while** loop (i.e.,  $b_{wh}$ ,  $b_3$ ,  $b_4$ ,  $b_5$ ), the corresponding nodes are associated with multiple  $C_{RWEC}(b_i)$  values, reflecting the maximum three iterations of the **while** loop.

With the  $C_{RWEC}(b_i)$  values computed, we can statically identify an edge  $(b_i,b_j)$  (of a CFG G) where  $[C_{RWEC}(b_i)-C_{EC}(b_i)] \neq C_{RWEC}(b_j)$ . For example, in Fig. 1(b), we can identify four such edges, i.e.,  $(b_1,b_2)$ ,  $(b_{wh},b_{if})$ ,  $(b_{if},b_7)$  and  $(b_3,b_5)$ , which are marked by the symbol  $\bullet$ . These marked edges form a set of candidate Voltage Scaling Edges (VSEs). If an edge  $(b_i,b_j)$  is selected as a VSE, it means that the clock speed will change when the thread of execution control branches to  $b_j$  from  $b_i$ . For example, the clock speed will be lowered when the basic block  $b_2$  is executed after  $b_1$  because the remaining work is reduced by 1/5 (i.e., the ratio of  $C_{RWEC}(b_2)$  to  $[C_{RWEC}(b_1)-C_{EC}(b_1)]$ ).

At the selected VSEs, the new clock speed is determined by how much the remaining work is reduced. For example, when the thread of execution control meets a VSE  $(b_i,b_j)$ , the clock speed can be lowered because the remaining work is reduced by  $[R-C_{RWEC}(b_j)]$  where  $R=C_{RWEC}(b_i)-C_{EC}(b_i)$ . After  $b_i$  is executed at the clock speed S, the clock speed can be changed to reflect the reduction in the remaining work. The new clock speed for  $b_j$  is set to  $S \times \frac{C_{RWEC}(b_j)}{R}$ . We call  $\frac{C_{RWEC}(b_j)}{R}$  as the speed update ratio (SUR) for the edge  $b_i \rightarrow b_j$ , denoted by  $SUR(b_i \rightarrow b_j)$ .

By the original IntraVS algorithm, the clock speed is changed from 80 MHz to 16 MHz (=  $80 \text{ MHz} \times \frac{30}{160-10}$ ) at the edge  $(b_1,b_2)$ . Assuming that no energy is consumed in an idle state and  $E \propto C_L \cdot$

$N_{cycle} \cdot V_{DD}^2$ , when the execution follows the path  $p_1 = (b_1, b_2, b_{if}, b_6, b_7)$ , the original IntraVS algorithm reduces the energy consumption by 69%.

Since there exists the transition overhead during speed changes, not all the candidate VSEs are selected as VSEs. A candidate VSE is selected as a VSE when the number of saved cycles at the candidate VSE is larger than a given threshold value. The threshold value is determined by a VSE selection policy, which is a function of the transition time overhead, the transition power overhead, and the code size increase (by the added scaling code).

# 3. PROFILE-BASED INTRA-TASK VOLTAGE SCHEDULING

### 3.1 Motivation

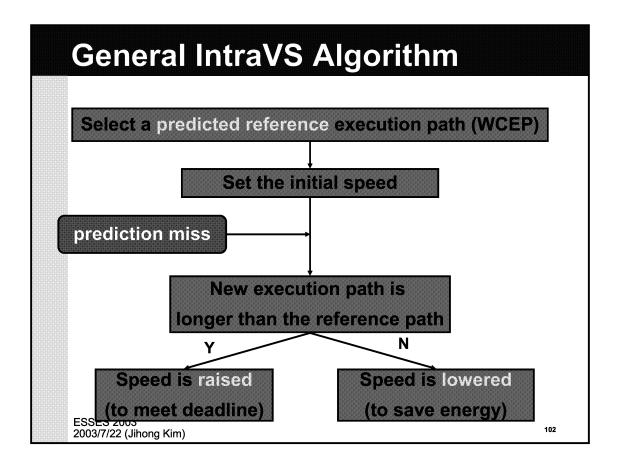

Before the profile-based IntraVS algorithm is presented, we first generalize the original IntraVS algorithm described in Section 2. In order to adjust the clock speed at VSEs, IntraVS first selects a (predicted) reference execution path such as the WCEP. Once the reference execution path is decided, IntraVS sets the initial operating voltage and its corresponding clock frequency assuming that the task execution will follow the predicted reference execution path.

When the actual execution deviates from the (predicted) reference execution path (say, by a branch instruction), the clock speed can be adjusted depending on the difference between the number of remaining execution cycles of the reference execution path and the number of remaining execution cycles of the newly deviated execution path. If the new execution path takes significantly longer to complete its execution than the reference execution path, the clock speed should be *raised* to meet the deadline constraint. On the other hand, if the new execution path can finish its execution earlier than the reference execution path, the clock speed can be *lowered* to save the energy consumption. Once the actual execution takes a different path from the reference path, a new reference path is constructed starting from the deviated basic block.

Using a static program-analysis technique, IntraVS identifies the appropriate program locations where the clock speed should be raised or lowered relative to the current clock speed. For the clock speed adjustment at run time, IntraVS algorithm inserts voltage scaling code to the selected program positions. The candidate positions for inserting voltage scaling code are the branching edges of the CFG, which correspond to the branch or loop statements.

We call the original IntraVS as the remaining worst-case execution path (RWEP)-based IntraVS, because the remaining worst-case execution path (RWEP) is used as the reference path. In the RWEP-based IntraVS, the clock speed is monotonically decreasing at all the VSEs. Depending on how the reference path is selected, however, the clock speed may be increased as well at some VSEs. Therefore, we divide VSEs into Up-VSEs and Down-VSEs. The clock speed is increased at an Up-VSE while the clock speed is decreased at a Down-VSE.

Although the RWEP-based IntraVS reduces the energy consumption significantly while guaranteeing the deadline, this is a pessimistic approach because it always predicts that the longest path will be executed. A more optimistic approach is to use the average case execution path (ACEP) as a reference path. The ACEP is defined to be an execution path that is most likely to be executed. The ACEP can be decided by the execution profile information.

The main motive of using the ACEP instead of the WCEP is to make the common case more energy-efficient. For a typical program, about 80 percent of the program's execution occurs in only 20 percent of its code, which is called the hot paths [1]. For an In-

traVS algorithm to be energy-efficient, it should be energy-efficient when the hot paths are executed. If we use one of hot paths as a reference path for intra-task voltage scheduling, the speed change graph for the hot paths will be a near flat curve with little changes in the clock speed, which gives the best energy efficiency under a given amount of work [3]. Even for the paths that are not the hot paths, if we take one of hot paths as a reference paths, they are more energy-efficient because they can start with a lower clock speed than when the WCEP is used as a reference path.

In the profile-based IntraVS, we take the ACEP, which is the best representative of the hot paths, as the reference path. We call such an IntraVS algorithm as the remaining average-case execution path (RAEP)-based IntraVS because the remaining average-case execution path (RAEP) is used as the reference path.

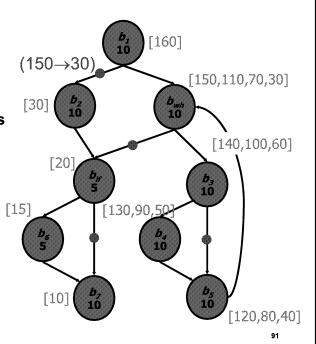

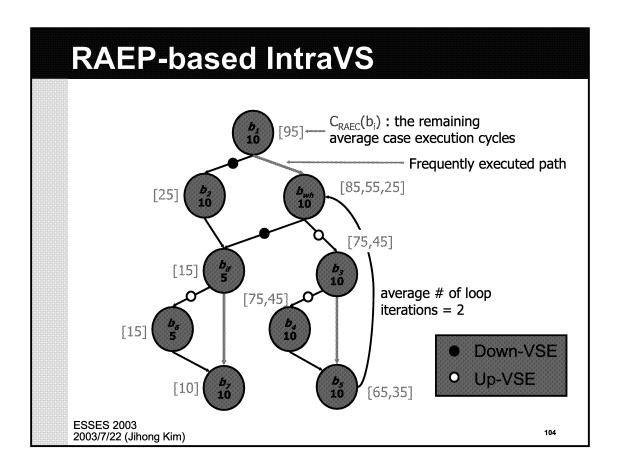

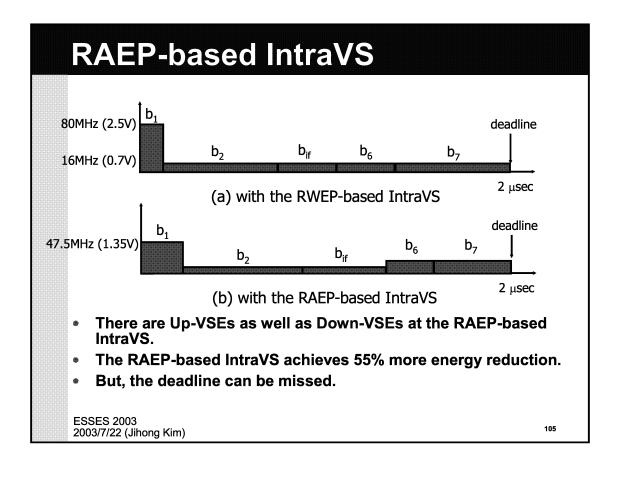

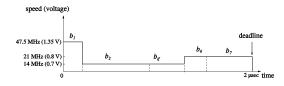

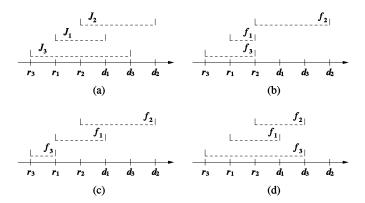

Figure 2 shows an RAEP-based CFG  $G_P^{RA\bar{E}P}$  with  $C_{RAEC}(b_i)$  values that represent the remaining average-case execution cycles among all the paths that start from  $b_i$ . The bold edges in  $G_P^{RAEP}$  means that it has a higher probability to be followed at run time between two branching edges. In Fig. 2, the initial reference path is  $(b_1,b_{wh},b_3,b_5,b_{wh},b_3,b_5,b_{wh},b_{if},b_7)$ . With the reference path,  $C_{RAEC}(b_i)$  is computed. For example,  $C_{RAEC}(b_{if}) = C_{EC}(b_{if}) + C_{RAEC}(b_7)$ . At the RAEP-based IntraVS, there are Up-VSEs (marked by  $\circ$  in Fig. 2) as well as Down-VSEs (marked by  $\circ$  in Fig. 2). Figure 3 shows how the speed and voltage change by the RAEP-based scheduling. The speed is changed from 14 MHz to 21 MHz at the edge  $(b_{if},b_6)$  because this is an Up-VSE with the SUR value of  $1.5 (= \frac{15}{15-5})$ . Compared to the energy consumption of the RWEP-based IntraVS algorithm, the RAEP-based IntraVS algorithm achieves 55% more energy reduction.

Figure 2: A RAEP-based CFG  $G_P^{RAEP}$ .

Figure 3: Speed and voltage changes by the RAEP-based IntraVS.

Though the RAEP-based scheduling is more effective in reducing the energy consumption than the RWEP-based scheduling, the pure RAEP-based approach cannot meet the timing requirements of hard real-time applications. This is because it dose not satisfy the timing constraint for all the execution paths. For example, consider the case when the WCEP and ACEP take significantly different number of execution cycles. When the execution takes the WCEP at the middle of program execution, it is possible that the program cannot meet its deadline even if the remaining path executes with the maximum clock speed. The next section describes a novel ap-

proach that is still based on the RAEC but can guarantee the timing constraint for all the execution paths.

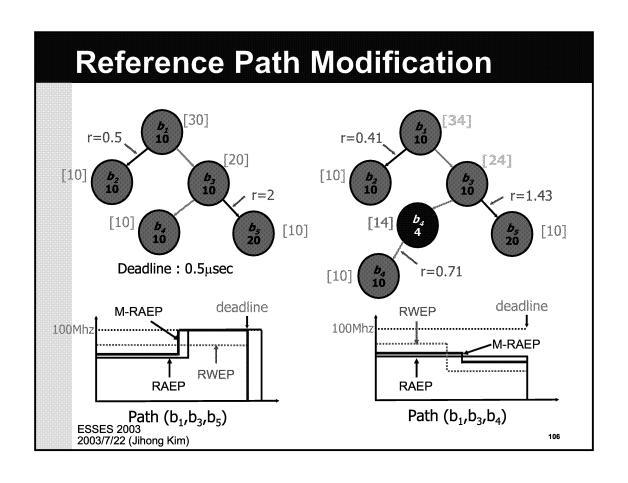

### 3.2 Reference Path Modification

To overcome the deadline miss problem of the pure RAEP-based IntraVS algorithm, we modify the reference path whenever the deadline miss situations are identified. Assume that the reference path is  $p_{ref} = (b_1, \cdots, b_i, b_{i+1}, \cdots, b_N), b_i$  is a branching node whose children basic blocks are  $b_{i+1}$  and  $b_{miss}$ , and the current clock speed at  $b_i$  is S. If the clock speed at  $b_{miss}$ , given by  $S \times SUR(b_i \rightarrow b_{miss})$ , is larger than the maximal clock speed (MaxS) of the processor, it indicates that if the current execution branches to  $b_{miss}$ , the deadline will be missed. This is because the remaining time  $T_R$  to the deadline is  $T_R = \frac{C_{RAEC}(b_{i+1})}{S}$  and  $MaxS \times T_R < C_{RAEC}(b_{miss})$ . There are  $M = [C_{RAEC}(b_{miss}) - MaxS \times T_R]$  cycles that miss the deadline. In order to avoid the deadline miss, we increment  $C_{RAEC}(b_k)$  by M for all  $k \le i$ . That is, we modify the reference path by adding a new virtual basic block  $b_v$  between  $b_i$  and  $b_{i+1}$ .  $C_{EC}(b_v)$  is set to M. The virtual basic block is used only to prevent the deadline miss during the speed assignment and not executed at run time.

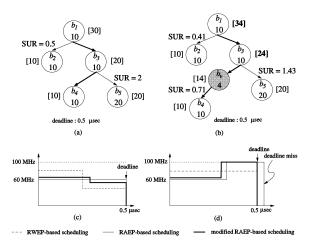

Figure 4 illustrates how the reference path modification works. Given an original  $G_P^{RAEP}$ , the ACEP,  $(b_1,b_3,b_4)$ , is used as the reference path. (The bold edges indicate higher probability edges to be selected at run time.) With the 100-MHz maximal clock frequency, the path  $(b_1,b_3,b_5)$  misses the 0.5- $\mu$ sec deadline, because the speed at  $(b_3,b_5)$  should be raised to 120 MHz (i.e., 60 MHz×2). Because  $\frac{10}{3}$  cycles are missed from the deadline, we add a virtual block  $b_V$  between  $b_3$  and  $b_4$ , as shown in Fig. 4(b).  $C_{EC}(b_V)$  is set to 4 (=  $\lceil \frac{10}{3} \rceil$ ).

With the added  $b_{\nu}$ ,  $C_{RAEC}(b_1)$  and  $C_{RAEC}(b_3)$  are modified to 34 and 24, respectively, and the speed update ratios are recalculated. For example, the SUR at  $(b_3,b_5)$  is modified to  $1.43 (= \frac{20}{14})$  from 2.

Figures 4(c) and 4(d) compare the speed changes for the RWEP-based IntraVS, the RAEP-based IntraVS and the modified RAEP-based IntraVS for the paths  $(b_1,b_3,b_4)$  and  $(b_1,b_3,b_5)$ , respectively. The modified RAEP-based scheduling is more energy-efficient than the RWEP-based scheduling for the hot paths (Fig. 4(c)), which affect most on the overall energy efficiency. It also satisfies the deadline requirement (Fig. 4(d)), unlike the pure RAEP-based scheduling algorithm.

### 4. EXPERIMENTAL RESULTS

We have extended the existing voltage scaling tool, the Automatic Voltage Scaler (AVS) [7], to evaluate the energy efficiency of the proposed IntraVS over the original IntraVS. AVS takes as inputs an original DVS-unaware program P and its timing requirements, and produces a low-energy DVS-aware program  $P_{DVS}$  that satisfies the same timing requirements of P. The converted program  $P_{DVS}$  contains voltage scaling code that handles all the idiosyncrasy of scaling speed/voltage on a variable voltage processor. The extended AVS can convert a program using either the RWEP-based IntraVS or the RAEP-based IntraVS.

To evaluate the power reduction effect of the proposed extensions to the original IntraVS algorithm, we have experimented with an MPEG-4 video decoder using an energy simulator [7]. We assume that both DVS-aware and DVS-unaware systems enter into a power-down mode when the system is idle. The energy consumption of a power-down mode is assumed to be 0. The supply voltage for a given clock frequency is obtained from  $f_{CLK} = 1/T_D \propto (V_{DD} - V_T)^{\alpha}/V_{DD}$  [6] where  $V_{DD}$ ,  $V_T$ , and  $\alpha$  are assumed to be 2.5V, 0.5V, and 1.3, respectively. For the RAEP-based IntraVS, the

$<sup>\</sup>overline{^{1}20 \text{ cycles} - 100 \text{ MHz} \times \frac{10}{60 \text{ MHz}}} = \frac{10}{3} \text{ cycles}$

Figure 4: Modified RAEP-based IntraVS: (a) an original  $G_P^{RAEP}$ , (b) a modified  $G_P^{RAEP}$ , and (c)-(d) the speed change graphs of three IntraVS algorithms for the paths  $(b_1,b_3,b_4)$  and  $(b_1,b_3,b_5)$ , respectively.

probability of branch edges and the average number of loop iterations in a CFG of the MPEG-4 video decoder are estimated using the profiled information. A probability of 0.5 is assigned to the branch edges for which we cannot collect the execution profiles with sample test bitstreams. For the experiments, the slew rate of the clock/voltage transition is assumed to be 1.0V/200µsec, which is typical for state-of-the-art DC-DC converters.

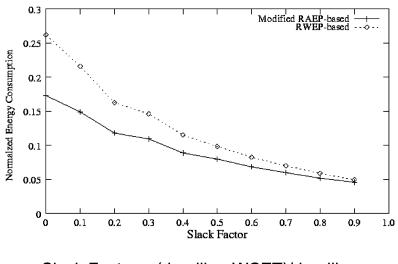

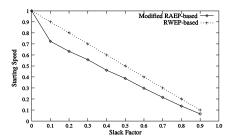

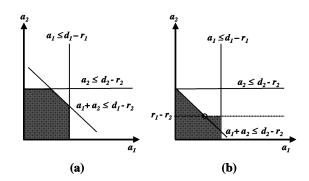

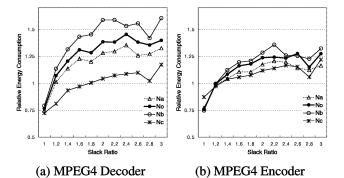

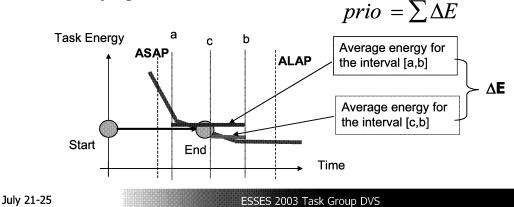

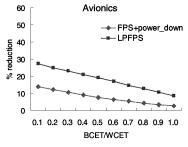

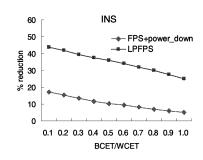

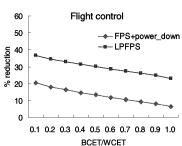

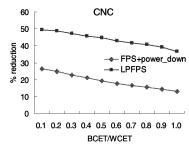

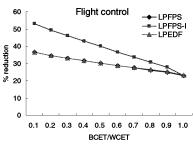

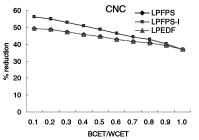

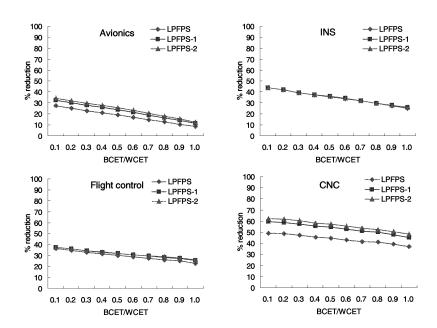

Figure 5: Normalized starting speed changes of the RWEP-based IntraVS and the RAEP-based IntraVS (varying the slack factor).

Figure 5 shows how the normalized starting speeds change over various slack factor values. The slack factor, defined by  $\frac{deadline-WCET}{deadline}$  represents the fraction of time that a processor becomes idle after WCET. The execution times of modified ACEPs (by the procedure described in Section 3.2) for the MPEG-4 decoder is up to 35% smaller than the WCET. This means that the processor can start initially 35% more slowly than the speed required by the RWEP-based IntraVS algorithm.

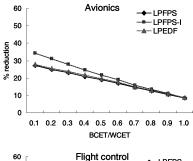

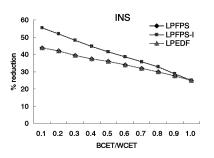

Figure 6 compares the energy consumption of two IntraVS scheduling algorithms, varying the slack factor. (All the results were normalized over the energy consumption of the original program running on a DVS-unaware system.) For the MPEG-4 decoder, the modified RAEP-based IntraVS algorithm reduces the energy consumption up to 34% over the RWEP-based IntraVS algorithm.

Note that there is a large gap between energy consumption of RWEP-based and RAEP-based IntraVS algorithms, even when the slack factor is 0 (i.e. deadline = WCET). This is because, although the starting speed is set to the same speed as in the RWEP-based IntraVS, there are many execution paths that still can take advan-

Figure 6: Normalized energy consumption of the RWEP-based IntraVS and RAEP-based IntraVS (varying the slack factor).

tage of the RAEP-based speed settings. That is, in order to meet the timing constraint, virtual blocks are added so that the initial speed is set to the same speed as in the RWEP-based IntraVS algorithm. However, the (partial) paths following the virtual blocks can take advantage of the ACEP-based speed settings. As the slack factor increases, the energy consumption gap decreases because supply voltages of both IntraVS algorithms get lower. Since the energy consumption is proportional to  $V_{DD}^2$ , the lower voltage values result in a smaller difference in the energy consumption.

### 5. CONCLUSION

We have presented a novel IntraVS algorithm based on the RAEP information. The proposed algorithm exploits the fact that the average-case execution paths are more likely to be followed at run time than the WCEP, and optimize the energy consumption for such hot paths. The main contribution of the proposed algorithm is that it enhances the original IntraVS algorithm by exploiting the probability of each execution path, while guaranteeing the worst-case timing constraints. The experimental results using an MPEG-4 video decoder show that the RAEP-based IntraVS improves the energy efficiency up to 34% over the RWEP-based IntraVS.

### 6. REFERENCES

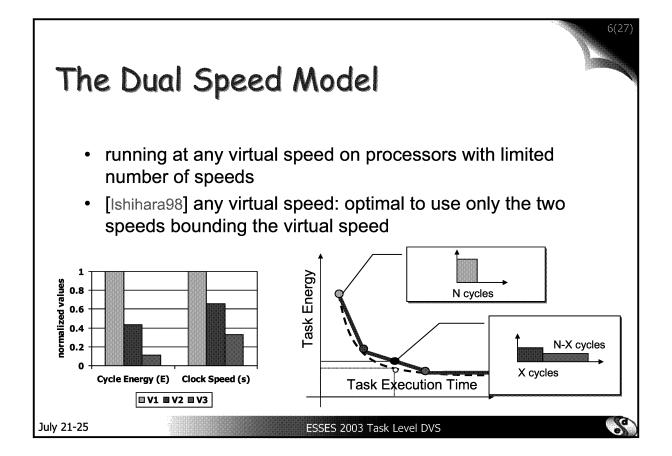

- [1] T. Ball and J. R. Larus. Using paths to measure, explain, and enhance program behavior. *IEEE Computer*, 33(7):57–65, 2000.

- [2] I. Hong, G. Qu, M. Potkonjak, and M. B. Srivastava. Synthesis techniques for low-power hard real-time systems on variable voltage processor. In *Proc. of the 19th IEEE Real-Time Systems Symposium*, pages 178–187, 1998.

- [3] T. Ishihara and H. Yasuura. Voltage scheduling problem for dynamically variable voltage processors. In Proc. of International Symposium On Low Power Electronics and Design, pages 197–202, 1998.

- [4] S. Lee and T. Sakurai. Run-time voltage hopping for low-power real-time systems. In *Proc. of the 37th Design Automation* Conference, pages 806–809, 2000.

- [5] Y. Lee and C. M. Krishna. Voltage-clock scaling for low energy consumption in real-time embedded systems. In *Proc. of the 6th International Conference on Real-Time Computing Systems and Applications*, pages 272–279, 1999.

- [6] T. Sakurai and A. Newton. Alpha-power law MOSFET model and its application to CMOS inverter delay and other formulas. *IEEE Journal of Solid State Circuits*, 25(2):584–594, 1990.

- [7] D. Shin, J. Kim, and S. Lee. Intra-task voltage scheduling for low-energy hard real-time applications. *IEEE Design and Test of Computers*, 18(2):20–30, 2001.

- [8] Y. Shin and K. Choi. Power conscious fixed priority scheduling for hard real-time systems. In *Proc. of the 36th Design Automation Conference*, pages 134–139, 1999.

- [9] F. Yao, A. Demers, and S. Shenker. A scheduling model for reduced CPU energy. In *Proc. of the 36th Annual Symposium on Foundations* of Computer Science, pages 374–382, 1995.

### An Opcode Encoding Method for Low-Power Instruction Fetch

Sunghwan Kim

Department of Computer Science Seoul National University Seoul, Korea 151-742 Tel: +82-2-880-5378 Fax: +82-2-871-4912

e-mail: shift@davinci.snu.ac.kr

Jihong Kim

Department of Computer Science Seoul National University Seoul, Korea 151-742 Tel: +82-2-880-8792

$Fax: \ +82\text{-}2\text{-}871\text{-}4912$ e-mail: jihong@davinci.snu.ac.kr

Abstract— In designing today's mobile embedded systems such as cellular phones and PDAs, power consumption is an important design constraint. In a CMOS circuit, switching activity accounts for over 90% of total power dissipation. In this paper, we describe a method of encoding opcodes for low-power instruction fetch by reducing the switching activity from the instruction fetch logic. To reduce the switching activity from the instruction-fetch logic, our method encodes opcodes so that more frequently consecutive instruction pairs have a smaller Hamming distance between their opcodes. Our experiment shows that the switching activity reduction of 36.4% to 66.7% is achievable over a naive encoding method.

#### I. Introduction

Power consumption has become a dominant design constraint for mobile embedded systems such as cellular phones and PDAs. In digital CMOS circuits (that use well-designed logic gates), switching activity accounts for over 90% of total power consumption [1]. Therefore, many techniques have been proposed and developed to reduce the amount of switching activity in multiple levels of design abstraction [2].

One papular approach widely used in reducing the switching activity is to encode digital values so that the number of bit changes by the values are reduced. For example, bus-invert coding tries to minimize the power dissipated in system bus by dynamically inverting the bus lines if the inversion reduces the number of bits switched on system bus [3]. Gray code addressing takes advantage of temporal redundancy in the instruction access patterns during program execution by using Gray-coded addresses as instruction addresses [4]. Register relabeling modifies the register number assignments so that more frequently consecutive register pairs have a smaller Hamming distance, reducing the switching activity in the register fields during instruction fetches and decodes [5].

In this paper, we describe a method of encoding opcodes for low-power instrucion fetches by reducing the

switching activity from the instruction fetch logic. Many redundant bit changes between consecutive instructions can be removed by encoding opcodes so that more frequently consecutive instruction pairs have a smaller Hamming distance between their opcodes. In principle, our method is similar to Gray code addressing [4] and register relabeling [5], in that digital values are statically encoded to minimize the number of bit changes by the values. However, we believe that this is the first attempt applying the low-power encoding scheme for the opcode encoding. For benchmark programs we tested, we were able to reduce the switching activity by 36.4% to 66.7% over a naive encoding method. We explain the opcode encoding method in Section III and report the experimental results in Section III.

#### II. LOW-POWER OPCODE ENCODING

#### A. Basic Idea