# An Evaluation Framework for Complex Industrial Real-Time Embedded Systems

Yue Lu, Thomas Nolte Mälardalen Real-Time Research Centre (MRTC), Västerås, Sweden yue.lu@mdh.se

*Abstract*—In this technical report, we introduce an evaluation framework which are centering around four base models, inspired by an industrial robotic control application. Specifically, such evaluation models are quite complicated from a task execution and temporal dependencies perspective, making difficult to perform the corresponding timing analysis.

## I. OVERVIEW

In today's world, industrial real-time embedded systems (IRTES) are becoming more and more complex. In fact, most of such systems tend to be probabilistic in nature, which makes difficult to perform the corresponding timing analysis. This technical report introduces an evaluation framework containing 32 evaluation models, which are inspired by one example of such IRTES. Specifically, in these evaluation models, there are interesting yet intricate task execution and temporal dependencies, such as asynchronous messagepassing and globally shared state variables, which may decide important control-flow conditions with major impact on task execution time as well as task response time and, 2) runtime changeability of priorities and periods of tasks and, 3) task offsets. In addition, our evaluation framework is running on a simulation framework RTSSim, which allows for simulating models describing the complicated control flow in tasks from both the functional and temporal behavior of systems. More details about RTSSim can be found in the following section. Finally, Section III describes the 32 evaluation models which are centering around four base models, in terms of system architecture, some interesting timing characteristics and the model source code in our simulation framework.

## **II. RTSSIM SIMULATION FRAMEWORK**

The evaluation framework in this work is described by the modeling language in the RTSSim simulation framework [1], which allows for simulating system models containing detailed intricate execution dependencies between tasks, such as asynchronous message-passing, globally shared state variables, and runtime changeability of priority and period of tasks. In RTSSim, the system consists of a set of tasks, sharing a single processor. RTSSim provides typical RTOS services to the simulation model, such as Fixed-Priority Preemptive Scheduling (FPPS), Inter-Process Communication (IPC) via message queues, and synchronization (semaphores). The tasks in a model are described by using C functions, which are called by the RTSSim framework. The framework provides an isolated "sandbox", where time is represented in a discrete manner using an integer simulation clock, which is only advanced explicitly by the tasks in the simulation model, using a special routine, *EXECUTE*. Calls to this routine models the tasks' consumption of CPU time.

All time-related operations in RTSSim, such as timeouts and activation of time-triggered tasks, are driven by the simulation clock, which makes the simulation result independent of process scheduling and performance of the analysis PC. The response time and execution time of tasks are measured whenever the scheduler is invoked, which happens for example at IPC, task switches, *EXECUTE* statements, operations on semaphores, task activations and when tasks end. This, together with the simulation clock behavior, guarantees that the measured response time and execution time are exact.

In RTSSim, a task may not be released for execution until a certain non-negative time (the offset) has elapsed after the arrival of the activating event. Each task also has a period, a maximum arrival jitter, and a priority. Periods and priorities can be changed at any time by any task in the application, and offset and jitter can both be larger than the period. Tasks with equal priorities are served on a first come first served basis. The framework allows for three types of selections which are directly controlled by simulator input data:

- selection of execution times (for EXECUTE),

- selection of task-arrival jitter,

- selection of task control flow, directly or indirectly based on environmental input stimulus.

In addition, Monte Carlo simulation can be realized by providing randomly generated (conforming to the uniform distribution) simulator input data, and gives output in terms of a set of traces, each of which contains the measured Response Time (RT) and Execution Time (ET) data of each task invocation during simulation.

#### **III. EVALUATION MODELS**

This section is split into three parts: Section III-A firstly introduces, in detail, the four base models, upon which the other evaluation models are. Next, Section III-B describes the variations of the base models which are developed by using system evolution scenarios, before the source code of the models in RTSSim is given in Section III-C.

### A. Four Base Models

As we mentioned previously, the evaluation framework consisting of 32 evaluation models, are based around four different base models, which are designed to include some behavioral mechanisms adopted by an industrial robotic control system. Specifically, the characteristics of the behavioral mechanisms in our evaluation models include intricate task execution and temporal dependencies, e.g., asynchronous message-passing by sending and receiving messages from buffers (as shown in lines 1 to 4 in Figure 1), execute statements representing some computation time taken by the (sub-)task (as shown in Line 6 in Figure 1), Global Shared State Variables (GSSVs) used in selecting control branches in tasks, runtime changeability of task priorities and periods (as shown in lines 8 to 13 in Figure 1), and task offsets. Moreover, we have applied system evolution scenarios (to be introduced in the following section) to these base models to create more evaluation models.

| 1 | <pre>msg = recvMessage(MyMessageQueue);</pre>  |

|---|------------------------------------------------|

| 2 | while (msg != NO_MESSAGE) {                    |

| 3 | process_msg(msg);                              |

| 1 | <pre>msg = recvMessage(MyMessageQueue);}</pre> |

| 5 |                                                |

| 5 | <pre>execute(for_some_time);</pre>             |

| 7 |                                                |

| 3 | if (GSSV1 == 1) {                              |

| ) | var1 = 10;                                     |

| ) | tcb->period = 20000;}                          |

| 1 | else{                                          |

| 2 | var2 = 5;                                      |

| 3 | tcb->period = 10000;}                          |

|   |                                                |

Figure 1. Iteration-loop wrt. message passing and GSSVs, and runtime changeability of task priorities and periods in the tasks in the industrial robotic control system evaluated in our work.

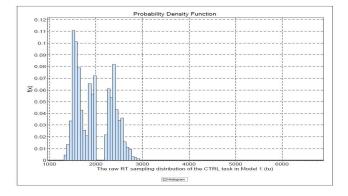

It is interesting to stress that due to the existence of intricate task execution and temporal dependencies in IRTES, an upcoming RT data may not be independent of the RT data previously recorded at the same system execution, for the same task. Furthermore, the timing behavior of the adhering tasks is also quite complicated. Figure 2 shows an example, i.e., given a large<sup>1</sup> number at sampling, the *Probability* Density Function (PDF) histogram of the CTRL task (i.e., the most important task under analysis) RT sample in the evaluation model MV4-1 (and the relevant model source code is shown in Section III-C4) is clearly conforming to a multi-modal distribution having several peaks. Particularly, because of such distinctive feature of our target CIRTES, it is difficult to bring conventional statistical methods [3] (e.g., t-test, z-test and analysis of variance (ANOVA)) into the context of predicting the worst-case timing behavior of the

Figure 2. The Probability Density Function (PDF) histogram of a RT sample of the CTRL task in MV4-1, i.e., the most complicated evaluation model.

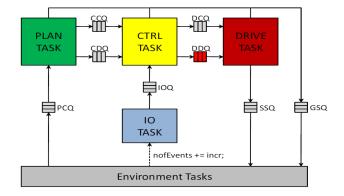

Figure 3. An industrial robotic control system architecture. From the view point of the number of queues, the main difference between MV4-\* and other evaluation models is that there is no Queue SSQ in the other models.

CTRL task in IRTES as shown in [4]. Since one important assumption, i.e., the underlying population is assumed to follow a normal distribution cannot be satisfied.

Besides, the four base models are designed to have increasing complexity. To be specific, the differences between these base models are mainly concerning the contained task execution and temporal dependencies as well as the number of sub-tasks, queues and GSSVs, which are increased from MV1 to MV4, as shown in Table I, making them more complex. The system architecture of the most complicated base model MV4, is shown in Figure 3.

### B. Model Variations Based upon System Evolution

In order to have a large number of evaluation models, we simply apply some typical system evolution scenarios to the four base models, each resulting in a set of new system models to analyze. In doing this, we either increase or decrease the execution time of sub-tasks in tasks in our base models, which reflects the scenarios of the change on system CPU speed. In practice, such scenarios can happen e.g., when the system is ported to a new hardware platform,

<sup>&</sup>lt;sup>1</sup>By running the evaluation model MV4-1 (which is one of the most interesting and complicated evaluation models) for the time up to the upper bound on the simulation time, i.e.,  $2^{31} - 1$ , we have collected 2 000 000 sample elements of the CTRL task RT population, of which the sample size is sufficiently enough to represent the underlying population [2].

Table I Models description and the relevant complexity. The lower numbered complexity is less complex, i.e., 1 stands for the simplest evaluation model.

| ModelsSub-tasksQueuesGSSVs |    |    | GSSVs | Description                                                                                                                                              | Complexity |

|----------------------------|----|----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| MV1*                       | 40 | 7  | 8     | IPC via the bounded<br>number of messages<br>and GSSVs, and task<br>offsets.                                                                             | 1          |

| MV2*                       | 42 | 7  | 8     | IPC via the bounded<br>number of messages<br>and GSSVs, and run-<br>time changeability of<br>priorities of tasks, and<br>task offsets.                   | 2          |

| MV3*                       | 42 | 7  | 8     | IPC via the bounded<br>number of messages<br>and GSSVs, and run-<br>time changeability of<br>priorities and periods<br>of tasks, and task off-<br>sets.  | 3          |

| MV4*                       | 59 | 12 | 10    | IPC via the<br>unbounded number<br>of messages and<br>GSSVs, and runtime<br>changeability of<br>priorities and periods<br>of tasks, and task<br>offsets. | 4          |

which thereby is upgraded or downgraded according to new design requirements.

- For the increase in system CPU speed, we limit ourselves to use 2, 5 and 10 as relevant factors in the work.

- For the decrease in system CPU speed, we limit ourselves to use 0.9, 0.8, 0.7 and 0.6 as relevant factors 27 in the work. It is worth noticing that a factor of 0.5 28 will result in the corresponding known best-practice 30 task WCRT longer than the corresponding task period, 31 i.e., if one would assume the deadline of a task to be 33 equal to its corresponding period, applying a factor of 34 0.5 would violate schedulability of the system. 36

Each of the factors highlighted above is marked as a  $\frac{37}{38}$  postfix to the model name, i.e., MV1-2 represents that the 39 CPU speed of the model variation MV1-2 is two times as  $\frac{40}{41}$  fast as the CPU speed of the model MV1; In other words, the corresponding execution time of sub-tasks in MV1-2 is 0.5 times as large as the corresponding ones in MV1.

To summarize, the task parameters used in these evaluation models are shown in Table II, where the *CTRL* task is the task under analysis, which is also the task with the most complicated timing behavior.

C. Pseudo Code of Our Evaluation Models

- 1) MV1 \*:

- 2) MV2 \*:

- 3) MV3-\*:

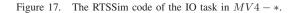

- 4) MV4 \*:

#### Table II

Tasks and task parameters for evaluation models. The lower numbered priority is more significant, i.e., 0 Stands For the highest priority. CTRL\_H and CTRL\_L represent the CTRL task with a higher and a lower priority respectively.

| Task   | Period (µs) | Offset (µs) | Priority | Models               |

|--------|-------------|-------------|----------|----------------------|

| DRIVE  | 2 000       | 12 000      | 2        | MV1-*, MV2-*, MV3-*, |

|        |             |             |          | MV4-*                |

| CTRL_H | 20 000      | 0           | 4        | MV2-*, MV3-*, MV4-*  |

| IO     | 5 000       | 500         | 5        | MV1-*, MV2-*, MV3-*, |

|        |             |             |          | MV4-*                |

| CTRL_L | 10 000      | 0           | 6        | MV1-*, MV2-*, MV3-*, |

|        |             |             |          | MV4-*                |

| PLAN   | 80 000      | 0           | 8        | MV1-*, MV2-*, MV3-*, |

|        |             |             |          | MV4-*                |

void DRIVE\_TASK(TCB\* tcb)

2

```

3

int msq;

4

msg = recvMessage(tcb, DDQ, 0);

5

execute(tcb, cDRIVEdecode);

6

7

switch (msg)

8

9

case MSG_SLC:

10

execute(tcb, cDRIVEslc);

11

if (ismoving == 0)

12

13

ismoving = 1;

14

15

break;

16

17

case MSG_SLCD:

18

execute(tcb, cDRIVEslcd);

19

if (ismoving == 1)

20

21

ismoving = 0;

22

23

break;

24

default:

break;

1

msg = recvMessage(tcb, DCO, 0);

if (msg > -1)

switch (msg)

case MSG GETSTS:

execute(tcb, cDRIVEgetsts);

sendMessage(tcb, GSQ, MSG_STS_DRIVE, FOREVER);

break;

37

default:

break;

}

}

```

Figure 4. The RTSSim code of the DRIVE task in MV1 - \*.

#### REFERENCES

- J. Kraft, "RTSSim A Simulation Framework for Complex Embedded Systems," Mälardalen University, Technical Report, Mar. 2009.

- D. S. Moore, G. P. Mccabe, and B. A. Craig, *Introduction to the practice of statistics*, 6th ed. New York, NY 10010: W. H. Freeman and Company, 2009.

- [3] "t-test and ANOVA, http://mathworld.wolfram.com, 2010."

```

1

void IO_TASK(TCB* tcb)

2

3

int status;

4

int eventsToProcess = 0;

5

6

7

if (nofEvents > 12)

{

8

eventsToProcess = 12;

9

}else{

10

eventsToProcess = nofEvents;

11

}

12

13

while(eventsToProcess-- > 0)

14

{

15

execute(tcb, cIOEvent);

16

nofEvents--;

17

status = sendMessage(tcb, IOQ, 1, 0);

18

}

19

}

```

Figure 5. The RTSSim code of the IO task in MV1 - \*.

Y. Lu, J. Kraft, T. Nolte, and I. Bate, "A statistical approach 24 to simulation model validation in response-time analysis of 25 complex real-time embedded systems," in *The 26th ACM* 27 Symposium on Applied Computing (SAC'11). ACM, Mar. 28 2011.

```

void CTRL_TASK(TCB* tcb)

1

2

3

int msg = -1;

4

int ioevent;

5

int i:

6

7

int nofIOEvents = 0;

.

8

9

msg = recvMessage(tcb, CCQ, 0);

execute(tcb, cCTRLdecode);

10

11

if (msg > -1)

12

{

13

switch (msg)

14

15

case MSG GETSTS:

16

sendMessage(tcb, DCQ, MSG_GETSTS, FOREVER);

17

execute(tcb, cCTRLgetsts);

sendMessage(tcb, GSQ, MSG_STS_CTRL, FOREVER);

18

19

break;

20

default:

21

break;

22

}

23

}

nofIOEvents = IOQ->current_size;

for (i=0; i < nofIOEvents; i++)</pre>

ioevent = recvMessage(tcb, IOQ, 0);

30

31

if (ioevent > -1)

32

{

33

execute(tcb, cCTRLioevent);

34

}

35

}

36

37

nSLC = 5;

38

tcb->period = 10000;

39

40

msg = recvMessage(tcb, CDQ, 0);

41

if (msg > -1)

42

{

43

switch(msg)

44

{

45

case MSG_FLC:

46

if (idle == 1)

47

{

48

idle = 0;

49

}

50

while (nSLC-- > 0)

51

{

execute(tcb,cCTRLslc);

sendMessage(tcb, DDQ, MSG_SLC, FOREVER);

52

53

54

1

55

break;

56

case MSG_LAST:

57

idle = 1;

execute(tcb,cCTRLlast);

58

59

break;

60

default:

61

break;

62

}

63

}

64

65

if (idle == 1)

66

{

67

while (nSLC-- > 0)

68

{

69

execute(tcb, cCTRLslcd);

70

sendMessage(tcb, DDQ, MSG_SLCD, FOREVER);

71

72

73

}

}

```

Figure 6. The RTSSim code of the CTRL task in MV1 - \*.

```

void PLAN_TASK(TCB* tcb) {

int nFLCs;

int cmd;

do

{

cmd = recvMessage(tcb, PCQ, 0);

execute(tcb, cPLANdecode);

if (cmd != -1)

{

switch(cmd)

case MSG_START:

remainingFLC = 50;

planstate = PLANSTATE_BEGIN;

execute(tcb, cPLANstart);

break;

case MSG_STOP:

planstate = PLANSTATE_IDLE;

execute(tcb, cPLANstop);

break;

case MSG GETSTS:

execute(tcb, cPLANgetsts);

sendMessage(tcb, GSQ, MSG_STS_PLAN, FOREVER);

sendMessage(tcb, CCQ, MSG_GETSTS, FOREVER);

break;

default:

break;

}

}while (cmd != -1);

switch (planstate)

case PLANSTATE BEGIN:

planstate = PLANSTATE_WORKING;

if (remainingFLC < CDQSIZE)

{

nFLCs = remainingFLC;

}else{

nFLCs = CDQSIZE;

while (nFLCs > 0)

{

execute(tcb, cPLANflc);

sendMessage(tcb,CDQ, MSG_FLC, FOREVER);

nFLCs--;

remainingFLC--;

break;

case PLANSTATE_WORKING:

if (remainingFLC < 4)

{

nFLCs = remainingFLC;

}else{

nFLCs = 4;

while (nFLCs > 0)

{

execute(tcb, cPLANflc);

sendMessage(tcb, CDQ, MSG_FLC, FOREVER);

nFLCs--;

remainingFLC--;

break;

case PLANSTATE_IDLE:

break;

}

if (

(remainingFLC <= 0 && planstate != PLANSTATE IDLE)

(remainingFLC > 0 && planstate == PLANSTATE_IDLE)

{

execute(tcb, cPlanLast);

planstate = PLANSTATE_IDLE;

remainingFLC = 0;

sendMessage(tcb, CDQ, MSG_LAST, FOREVER);

}

```

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57 58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77 78

79

80

81 }

```

1

void DRIVE_TASK(TCB* tcb)

int msq;

msg = recvMessage(tcb, DDQ, 0);

execute(tcb, cDRIVEdecode);

if (DDQ->current_size < MINDDQSIZE)

{

TCB* ctrl_task = findTCBbyName("CTRL_TASK");

ctrl_task->prio = 2;

execute(tcb, cDRIVEet200);

}else{

TCB* ctrl_task = findTCBbyName("CTRL_TASK");

ctrl_task->prio = 4;

execute(tcb, cDRIVEet100);

}

switch(msg)

{

case MSG_SLC:

execute(tcb, cDRIVEslc);

if (ismoving == 0)

{

ismoving = 1;

}

break;

case MSG SLCD:

execute(tcb, cDRIVEslcd);

if (ismoving == 1)

ismoving = 0;

break;

default:

break;

}

msg = recvMessage(tcb,DCQ,0);

if (msg > -1)

{

switch(msg)

case MSG GETSTS:

execute(tcb, cDRIVEgetsts);

sendMessage(tcb,GSQ,MSG_STS_DRIVE,FOREVER);

break;

default:

break;

}

}

51 }

```

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

Figure 8. The RTSSim code of the DRIVE task in MV2 - \*.

```

void IO_TASK(TCB* tcb)

int status;

int eventsToProcess = 0;

if (nofEvents > 12)

{

eventsToProcess = 12;

}else{

eventsToProcess = nofEvents;

}

while (eventsToProcess-- > 0)

{

execute(tcb, cIOEvent);

nofEvents--;

status = sendMessage(tcb, IOQ, 1, 0);

}

19 }

```

Figure 9. The RTSSim code of the IO task in MV2 - \*.

Figure 7. The RTSSim code of the PLAN task in MV1 - \*.

```

void CTRL TASK(TCB* tcb)

1

2

3

int msg = -1;

4

int ioevent;

5

int i;

6

int nofIOEvents = 0;

7

8

msg = recvMessage(tcb, CCQ, 0);

9

execute(tcb, cCTRLdecode);

10

11

if (msg > -1)

12

13

switch (msg)

14

15

case MSG_GETSTS:

16

sendMessage(tcb, DCQ, MSG_GETSTS, FOREVER);

17

execute(tcb, cCTRLgetsts);

18

sendMessage(tcb, GSQ, MSG_STS_CTRL, FOREVER);

19

break;

20

default:

21

break;

22

}

\bar{23}

}

24

25

nofIOEvents = IOQ->current_size;

26

for (i = 0; i < nofIOEvents; i++)</pre>

27

28

ioevent = recvMessage(tcb, IOQ, 0);

29

30

if (ioevent > -1)

31

{

32

execute(tcb, cCTRLioevent);

33

}

34

}

35

36

nSLC = 5;

37

tcb->period = 10000;

38

msg = recvMessage(tcb, CDQ, 0);

39

if (msg > -1)

40

{

41

switch(msg)

42

43

case MSG FLC:

44

if (idle == 1)

45

{

46

idle = 0:

47

48

while (nSLC - > 0)

49

{

50

execute(tcb,cCTRLslc);

51

sendMessage(tcb, DDQ, MSG_SLC, FOREVER);

52

53

break:

54

case MSG_LAST:

55

idle = 1;

56

execute(tcb, cCTRLlast);

57

break;

58

default:

59

break;

60

}

61

}

62

63

if (idle == 1)

64

{

65

while (nSLC-- > 0)

66

67

execute(tcb, cCTRLslcd);

68

sendMessage(tcb, DDQ, MSG_SLCD, FOREVER);

69

70

}

71

}

```

Figure 10. The RTSSim code of the CTRL task in MV2 - \*.

```

void PLAN_TASK(TCB* tcb){

int nFLCs;

int cmd;

do

cmd = recvMessage(tcb, PCQ, 0);

execute(tcb, cPLANdecode);

if (cmd != -1)

switch(cmd)

case MSG_START:

remainingFLC = 50;

planstate = PLANSTATE_BEGIN;

execute(tcb, cPLANstart);

break;

case MSG_STOP:

planstate = PLANSTATE_IDLE;

execute(tcb, cPLANstop);

break;

case MSG GETSTS:

execute(tcb, cPLANgetsts);

sendMessage(tcb, GSQ, MSG_STS_PLAN, FOREVER);

sendMessage(tcb, CCQ, MSG_GETSTS, FOREVER);

break;

default:

break;

}

}while (cmd != -1);

switch (planstate)

case PLANSTATE BEGIN:

planstate = PLANSTATE_WORKING;

if (remainingFLC < CDQSIZE)

nFLCs = remainingFLC;

}else{

nFLCs = CDQSIZE;

while (nFLCs > 0)

{

execute(tcb, cPLANflc);

sendMessage(tcb, CDQ, MSG_FLC, FOREVER);

nFLCs--;

remainingFLC--;

break;

case PLANSTATE_WORKING:

if (remainingFLC < 4)

nFLCs = remainingFLC;

}else{

nFLCs = 4;

while (nFLCs > 0)

{

execute(tcb, cPLANflc);

sendMessage(tcb, CDQ, MSG_FLC, FOREVER);

nFLCs--;

remainingFLC--;

break;

case PLANSTATE_IDLE:

break;

}

if (

(remainingFLC <= 0 && planstate != PLANSTATE IDLE)

(remainingFLC > 0 && planstate == PLANSTATE_IDLE)

)

{

execute(tcb, cPlanLast);

planstate = PLANSTATE_IDLE;

remainingFLC = 0;

sendMessage(tcb, CDQ, MSG_LAST, FOREVER);

}

```

2

3

4

5 6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32 33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81 }

```

void DRIVE_TASK(TCB* tcb)

1

2

3

int msg;

msg = recvMessage(tcb, DDQ, 0);

5

execute(tcb, cDRIVEdecode);

6

if (DDQ->current_size < MINDDQSIZE)

9

TCB* ctrl_task = findTCBbyName("CTRL_TASK");

10

ctrl_task -> prio = 2;

11

ctrl_task->period = 20000;

12

}else{

13

TCB* ctrl_task = findTCBbyName("CTRL_TASK");

ctrl_task->prio = 4;

14

ctrl_task->period = 10000;

15

16

}

17

18

switch(msg)

19

{

20

case MSG_SLC:

execute(tcb, cDRIVEslc);

21

if (ismoving == 0)

24

ismoving = 1;

25

26

break;

27

28

case MSG_SLCD:

29

execute(tcb, cDRIVEslcd);

30

if (ismoving == 1)

{

ismoving = 0;

33

break;

default:

36

break;

}

39

msg = recvMessage(tcb,DCQ,0);

40

if (msg > -1)

{

switch(msg)

{

case MSG_GETSTS:

execute(tcb, cDRIVEgetsts);

sendMessage(tcb,GSQ,MSG_STS_DRIVE,FOREVER);

break;

default:

49

break;

50

}

}

52

```

7

8

22

31

32

34

35

37

38

41

42

43

44

45

46

47

48

51

}

Figure 12. The RTSSim code of the DRIVE task in MV3 - \*.

```

1 void IO_TASK(TCB* tcb)

2

3

int status;

4

int eventsToProcess = 0;

5

6

7

if (nofEvents > 12)

{

8

eventsToProcess = 12;

9

}else{

10

eventsToProcess = nofEvents;

11

}

12

13

while(eventsToProcess-- > 0)

14

{

15

execute(tcb, cIOEvent);

16

nofEvents--;

17

status = sendMessage(tcb, IOQ, 1, 0);

18

}

19

}

```

1 void CTRL\_TASK(TCB\* tcb) int msg = -1;int icevent; int i; int nofIOEvents = 0; msg = recvMessage(tcb, CCQ, 0); execute(tcb, cCTRLdecode ); if (msg > -1){ switch (msg) { case MSG\_GETSTS: sendMessage(tcb, DCQ, MSG\_GETSTS, FOREVER); execute(tcb,cCTRLgetsts); sendMessage(tcb, GSQ, MSG\_STS\_CTRL, FOREVER); break; default: break: } } nofIOEvents = IOQ->current\_size; for (i=0; i < nofIOEvents; i++)</pre> ioevent = recvMessage(tcb, IOQ, 0); if (ioevent > -1) { execute(tcb, cCTRLioevent); } } nSLC = 5; $tcb \rightarrow period = 10000;$ msg = recvMessage(tcb, CDQ, 0); if (msg > -1){ switch(msg) case MSG\_FLC: if (idle == 1) { idle = 0;while (nSLC - > 0){ execute(tcb,cCTRLslc); sendMessage(tcb, DDQ, MSG\_SLC, FOREVER); break; case MSG\_LAST: idle = 1; execute(tcb,cCTRLlast); break; default: break; } } if (idle == 1) while (nSLC-- > 0) execute(tcb,cCTRLslcd); sendMessage(tcb, DDQ, MSG\_SLCD, FOREVER); }

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

$\bar{23}$

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55 56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74 }

Figure 13. The RTSSim code of the IO task in MV3 - \*.

Figure 14. The RTSSim code of the CTRL task in MV3 - \*.

```

void PLAN_TASK(TCB* tcb)

int nFLCs;

int cmd;

do

cmd = recvMessage(tcb, PCQ, 0);

execute(tcb, cPLANdecode);

if (cmd != -1)

{

switch(cmd)

case MSG_START:

remainingFLC = 50;

planstate = PLANSTATE_BEGIN;

execute(tcb, cPLANstart);

break;

case MSG_STOP:

planstate = PLANSTATE_IDLE;

execute(tcb, cPLANstop);

break;

case MSG_GETSTS:

execute(tcb, cPLANgetsts);

sendMessage(tcb, GSQ, MSG_STS_PLAN, FOREVER);

sendMessage(tcb, CCQ, MSG_GETSTS, FOREVER);

break;

default:

break;

}

while (cmd != -1);

switch (planstate)

case PLANSTATE BEGIN:

planstate = PLANSTATE_WORKING;

if (remainingFLC < CDQSIZE)

nFLCs = remainingFLC;

}else{

nFLCs = CDQSIZE;

while (nFLCs > 0)

{

execute(tcb, cPLANflc);

sendMessage(tcb,CDQ, MSG_FLC, FOREVER);

nFLCs--;

remainingFLC--;

break;

case PLANSTATE_WORKING:

if (remainingFLC < 4)

{

nFLCs = remainingFLC;

}else{

nFLCs = 4;

while (nFLCs > 0)

{

execute(tcb, cPLANflc);

sendMessage(tcb,CDQ, MSG_FLC, FOREVER);

nFLCs--;

remainingFLC--;

break;

case PLANSTATE_IDLE:

break;

}

if (

(remainingFLC <= 0 && planstate != PLANSTATE_IDLE)</pre>

(remainingFLC > 0 && planstate == PLANSTATE_IDLE)

)

{

execute(tcb, cPlanLast);

planstate = PLANSTATE_IDLE;

remainingFLC = 0;

sendMessage(tcb, CDQ, MSG_LAST, FOREVER);

}

```

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80 81

82 }

```

void DRIVE_TASK(TCB* tcb)

int msq;

msg = recvMessage(tcb, DDQ, 0);

execute(tcb, cDRIVEdecode);

if (DDQ->current_size < MINDDQSIZE)

TCB* ctrl_task = findTCBbyName("CTRL_TASK");

ctrl_task->prio = 2;

}else{

TCB* ctrl_task = findTCBbyName("CTRL_TASK");

ctrl_task->prio = 4;

}

switch(msg)

{

case MSG_SLC:

execute(tcb, cDRIVEslc);

if (ismoving == 0)

{

ismoving = 1;

sendMessage(tcb, SSQ, MSG_MOVING, FOREVER);

break;

case MSG SLCD:

execute(tcb, cDRIVEslcd);

if (ismoving == 1)

ismoving = 0;

sendMessage(tcb, SSQ, MSG_NOTMOVING, FOREVER);

break;

default:

break;

}

msg = recvMessage(tcb,DCQ,0);

if (msg > -1)

{

switch(msg)

case MSG GETSTS:

execute(tcb, cDRIVEgetsts);

sendMessage(tcb, GSQ, MSG_STS_DRIVE, FOREVER);

break;

default:

break;

}

}

51 }

```

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

2

3

4

6

7

8

9

10

11

12

13

14

15

16

17

18

Figure 16. The RTSSim code of the DRIVE task in MV4 - \*.

```

void IO_TASK(TCB* tcb)

int status;

int eventsToProcess = 0;

if (nofEvents > 12)

{

eventsToProcess = 12;

}else{

eventsToProcess = nofEvents;

}

while (eventsToProcess-- > 0)

{

execute(tcb, cIOEvent);

nofEvents--;

status = sendMessage(tcb, IOQ, 1, 0);

}

19 }

```

```

1

void CTRL_TASK(TCB* tcb)

2

3

int msg;

4

int ioevent;

5

int i;

6

7

msg = recvMessage(tcb, CCQ, 0);

execute(tcb, cCTRLdecode);

8

9

if (msg > -1)

10

{

11

switch (msg)

12

{

13

case MSG_GETSTS:

14

sendMessage(tcb, DCQ, MSG_GETSTS, FOREVER);

15

execute(tcb, cCTRLgetsts);

16

sendMessage(tcb, GSQ, MSG_STS_CTRL, FOREVER);

17

break;

18

default:

19

break;

20

}

21

}

22

i = 0;

23

do{

24

ioevent = recvMessage(tcb, IOQ, 0);

25

if (ioevent > -1)

26

{ i++;

27

execute(tcb, cCTRLioevent);}

28

}while (icevent > -1);

29

30

if (closeToTarget == 1) {

31

nSLC = 10;

32

tcb->period = 20000;

33

} else {

34

nSLC = 5;

35

tcb->period = 10000;

36

}

37

38

msg = recvMessage(tcb, CDQ, 0);

39

if (msg > -1)

40

{

41

switch(msg)

42

43

{

case MSG_FLC:

44

if (idle == 1)

45

{

46

idle = 0;

47

48

while (nSLC-- > 0)

49

{

50

51

52

execute(tcb,cCTRLslc);

sendMessage(tcb, DDQ, MSG_SLC, FOREVER);

}

53

54

55

56

break;

case MSG_LAST:

idle = 1;

closeToTarget = 0;

57

execute(tcb, cCTRLlast);

58

break;

59

default:

60

break;

61

}

62

}

63

64

if (idle == 1)

65

{

66

while (nSLC-- > 0)

67

{

68

execute(tcb,cCTRLslcd);

69

sendMessage(tcb, DDQ, MSG_SLCD, FOREVER);

70

1

71

}

72

}

```