Mälardalen University Press Dissertations No. 170

## SOFTWARE AND HARDWARE MODELS IN COMPONENT-BASED DEVELOPMENT OF EMBEDDED SYSTEMS

Luka Lednicki

2015

University of Zagreb Faculty of Electrical Engineering and Computing

School of Innovation, Design and Engineering

Copyright © Luka Lednicki, 2015 ISBN 978-91-7485-180-9 ISSN 1651-4238 Printed by Arkitektkopia, Västerås, Sweden Mälardalen University Press Dissertations No. 170

### SOFTWARE AND HARDWARE MODELS IN COMPONENT-BASED DEVELOPMENT OF EMBEDDED SYSTEMS

Luka Lednicki

Akademisk avhandling

som för avläggande av teknologie doktorsexamen i datavetenskap vid Akademin för innovation, design och teknik kommer att offentligen försvaras tisdagen den 27 januari 2015, 13.00 i Gamma, Högskoleplan 1, Västerås.

Fakultetsopponent: Professor Martin Törngren, KTH Royal Institute of Technology

University of Zagreb Faculty of Electrical Engineering and Computing

School of Innovation, Design and Engineering

#### Abstract

As modern embedded systems grow in complexity component-based development is an increasingly attractive approach to make the development of such systems simpler and less error prone. In this approach software systems are built by composing them out of prefabricated software components. One of the challenges for applying component-based development to embedded systems is the tight coupling between the software and the hardware platform. To take full advantage of the component-based approach in the embedded domain, the development process has to provide support for describing and handling this coupling.

The goal of this thesis is to provide advancements in development of embedded component-based systems by using a combination of software and hardware models. To achieve the overall research goal, three different aspects are investigated: (i) how to provide support for integration of sensors and actuators in component-based development, (ii) how to utilize a combination of software and hardware models in development of distributed systems, and (iii) how to analyze extra-functional system properties using models of both software and hardware. The thesis goal is addressed by following contributions: (i) a component-based model which allows describing sensors and actuators, and how they are connected to the processing nodes and software components, (ii) a method for automatic synthesis of code for communication with sensors and actuators, (iii) a framework for automatic generation of distributed communication, by applying prototype tools to either example systems, case-studies, or test scenarios.

This thesis is presented in partial fulfillment of international dual doctoral degree at Faculty of Electrical Engineering and Computing, University of Zagreb, Croatia, and School of Innovation, Design and Engineering, Mälardalen University, Sweden.

#### Main advisors

Prof. Ivica Crnković, Mälardalen University, Sweden Prof. Mario Žagar, University of Zagreb, Croatia

**Co-advisor** Associate Prof. Jan Carlson, Mälardalen University, Sweden

Faculty examiner

Prof. Martin Törngren, KTH Royal Institute of Technology, Sweden

#### Examining committee

Associate Prof. Tomáš Bureš, Charles University in Prague, Czech Republic Associate Prof. Željka Car, University of Zagreb, Croatia Dr. Roland Weiss, ABB Corporate Research, Germany

To my family

## Abstract

As modern embedded systems grow in complexity component-based development is an increasingly attractive approach to make the development of such systems simpler and less error prone. In this approach software systems are built by composing them out of prefabricated software components. One of the challenges for applying component-based development to embedded systems is the tight coupling between the software and the hardware platform. To take full advantage of the componentbased approach in the embedded domain, the development process has to provide support for describing and handling this coupling.

The goal of this thesis is to provide advancements in development of embedded component-based systems by using a combination of software and hardware models. To achieve the overall research goal, three different aspects are investigated: (i) how to provide support for integration of sensors and actuators in component-based development, (ii) how to utilize a combination of software and hardware models in development of distributed systems, and (iii) how to analyze extra-functional system properties using models of both software and hardware. The thesis goal is addressed by following contributions: (i) a component-based model which allows describing sensors and actuators, and how they are connected to the processing nodes and software components, (ii) a method for automatic synthesis of code for communication with sensors and actuators, (iii) a framework for automatic generation of distributed communication in component-based models and (iv) a compositional model-level analysis of timing and processing node utilization for component-based applications. These contributions are evaluated in separation, by applying prototype tools to either example systems, case-studies, or test scenarios.

## Prošireni sažetak

#### Programski i sklopovski modeli u razvoju ugradbenih sustava utemeljenih na programskim komponentama

Povećanjem složenost modernih ugradbenih sustava u njihovom razvoju se sve češće pokušava primijeniti pristup temeljen na programskim komponentama. Koristeći ovaj pristup sustavi se izrađuju sastavljanjem programskih komponenata – već postojećih elemenata namijenjenih višestrukom korištenju. Ovakav način razvoja može, između ostalog, znatno skratiti vrijeme izrade sustava, smanjiti količinu grešaka u sustavu te učiniti sustave predvidljivijima. Jedan od aspekata ključnih u razvoju ugradbenih sustava je visok stupanj povezanosti programske podrške i sklopovlja. Iako postoje mnoge metode koje omogućuju modeliranje sklopovlja i olakšavaju razvoj programske podrške specifične za sklopovlje, one su rijetko integrirane s metodama razvoja temeljenim na komponentama.

Cilj ovog rada je unaprijediti proces razvoja ugradbenih sustava temeljen na programskim komponentama koristeći kombinaciju programskih i sklopovskih modela. U okviru rada istražena su tri aspekta razvoja: (i) kako pružiti podršku za integraciju senzora i aktuatora u razvoju temeljenom na programskim komponentama, (ii) kako unaprijediti razvoj raspodjeljenih sustava koristeći modele programske podrške i modele sklopovlja te (iii) kako analizirati svojstva sustava upotrebom spomenutih modela. Cilj rada ostvaren je sljedećim doprinosima:

- **Doprinos 1** Model ugradbenog sustava temeljen na programskim komponentama koji uključuje senzore i aktuatore,

- Doprinos 2 Metoda sinteze programskog koda iz predloženog komponentnog modela,

- Doprinos 3 Metoda automatskog generiranja komunikacijskih komponenata u modelima raspodjeljenih ugradbenih sustava,

- Doprinos 4 Metoda kompozicijske analize vremenskih karakteristika i opterećenja procesnih čvorova u sustavima temeljenim na programskim komponentama.

Doprinos 1 proširuje postojeći komponentni model ProCom mogućnošću opisivanja senzora i aktuatora. Osim samog opisa senzora i aktuatora, novi model omogućuje i specificiranje načina na koji su ovi uređaji spojeni na procesne čvorove sustava. Postojeće programske komponente modela ProCom proširene su opisom ovisnosti o senzorima i aktuatorima. Veze između programske podrške i sklopovlja opisuju se pridruživanjem elemenata modela sklopovlja ovisnostima programskih komponenata. Predloženi model promiče ponovno korištenje jednom razvijenih elemenata jasnim razdvajanjem onih elemenata koji su neovisni o kontekstu od elemenata koji su specifični za pojedini sustav. U svrhu evaluacije model je implementiran u okviru prototipnog alata i primjenjen na realistični primjer, čime je pokazano da je pristup prikladan za modeliranje stvarnih sustava.

U okviru doprinosa 2 razvijena je metoda koja na temelju modela predloženog u doprinosu 1 automatski stvara programski kôd za komunikaciju programskih komponenata sa senzorima i aktuatorima. Metoda definira dvije grupe elemenata programskog koda: *ulazne elemente* i *izlazne elemente*. Ulazni elementi podobni su za višestruko korištenje te se pridružuju elementima modela koji su neovisni o kontekstu. Izlazni elementi koda stvaraju se automatski, na temelju elemenata modela specifičnih za sustav. Dobivena kombinacija ulaznih i izlaznih elemenata pruža potpunu komunikaciju između programskih komponenata i sklopovlja. Doprinos je evaluiran primjenom prototipnog alata na realistični primjer. Rezultati evaluacije pokazali su da generirani kôd pruža točnu implementaciju komunikacije. Evaluacija je također obuhvatila mjerenje povećanja vremena izvođenja i zauzeća memorije dobivenog kôda.

Doprinos 3 čini razvojni okvir koji omogućuje automatsko stvaranje komunikacije između čvorova raspodijeljenih aplikacija temeljenih na programskim komponentama. Komunikacija se implementira dodavanjem programskih komponenata u modele aplikacije specifične za pojedine čvorove sustava. Ove komponente stvaraju se na temelju modela aplikacije neovisnog o sklopovlju sustava i modela koji opisuje sklopovlje. Razvojni okvir podijeljen je u module, međusobno povezane samo unaprijed definiranim sučeljima, čime se olakšavaju prilagođavanje metode različitim komponentnim modelima i nadogradnja okvira novim mogućnostima. Razvojni okvir je primijenjen na normu IEC 61499 te je implementiran prototipni alat. Evaluacija doprinosa izvršena je primjenom razvojnog okvira na prošireni primjer i na dvije studije slučaja. Modeli dobiveni automatskim stvaranjem bili su u skladu s očekivanim rezultatima, dok je dobivena komunikacija ispravno implementirala funkcionalnost sustava.

Doprinos 4 ovoga rada je metoda analize svojstava sustava izrađenih normom IEC 61499. Predložena metoda analize podjeljena je na dva dijela: analizu najdužeg vremena izvođenja i analizu opterećenja procesnih čvorova. Izračun najdužeg vremena izvođenja dijelova aplikacije temelji se na konceptu kompozicije komponenata. Analiza opterećenja procesnih čvorova omogućena je proširenjem analize najdužeg vremena izvođenja, u isto vrijeme uzimajući u obzir i modele sklopovlja. Za obje metode analize implementirani su prototipni alati. Isti alati su upotrijebljeni u svrhu evaluacije, primjenjujući ih na primjere preuzete iz dva postojeća alata za razvoj sustava pomoću norme IEC 61499. Dijelovi analize također su evaluirani primjenom prototipnog alata na skup testova. Evaluacija je pokazala da je predložena analiza primijenjiva na stvarne sustave te da algoritmi analize imaju visoku učinkovitost. Rezultati testova pokazali su ispravnost pojedinih dijelova analize.

## Acknowledgements

I would like to start the acknowledgements with two persons who gave me the opportunity to be a PhD student, my advisors Mario Žagar and Ivica Crnković. Thank you for guiding me, pushing me forward, and providing both professional and personal support whenever I needed it. An equal amount of thanks also goes to my co-advisor Jan Carlson. All discussions, advice and detailed comments have certainly made this a better thesis, and made me a better researcher.

During these years of doctoral studies I have worked with many people from both Croatian and Swedish universities. With your willingness to help, friendship, and remarkable coffee-drinking skills you have made the university more than just a work place. Thank you for that! I will not try to list you all here, you know who you are!

To my parents Blanka and Damir, and sister Iva, thank you for providing endless support and encouraging me to achieve more through all my life. Without you I surely wouldn't be here, writing acknowledgments for a doctoral dissertation.

Lastly, Anna, you were by my side through all these years, you supported me when I needed it, and you made my life more interesting and fun than I could have imagined! Thank you!

Luka Lednicki Västerås, December 2014

This work was partly supported by the Unity Through Knowledge Found through project project DICES, Swedish Foundation for Strategic Research via research centre PROGRESS and through project RALF3, and ABB Software Research Grant Program through project ASSIST.

# Contents

| 1            | Intr | Introduction                                            |  |  |  |  |  |

|--------------|------|---------------------------------------------------------|--|--|--|--|--|

|              | 1.1  | Research questions                                      |  |  |  |  |  |

|              | 1.2  | Contributions                                           |  |  |  |  |  |

|              | 1.3  | Research methodology                                    |  |  |  |  |  |

|              | 1.4  | Publications                                            |  |  |  |  |  |

|              |      | 1.4.1 Main contributing publications                    |  |  |  |  |  |

|              |      | 1.4.2 Other related publications                        |  |  |  |  |  |

|              | 1.5  | Thesis outline                                          |  |  |  |  |  |

| 2 Background |      |                                                         |  |  |  |  |  |

|              | 2.1  | ProCom                                                  |  |  |  |  |  |

|              |      | 2.1.1 Components                                        |  |  |  |  |  |

|              |      | 2.1.2 Component types                                   |  |  |  |  |  |

|              |      | 2.1.3 Semantics                                         |  |  |  |  |  |

|              |      | 2.1.4 Platform modeling and deployment                  |  |  |  |  |  |

|              |      | 2.1.5 Analysis                                          |  |  |  |  |  |

|              | 2.2  | IEC 61499                                               |  |  |  |  |  |

|              |      | 2.2.1 Components                                        |  |  |  |  |  |

|              |      | 2.2.2 Component types                                   |  |  |  |  |  |

|              |      | 2.2.3 Semantics                                         |  |  |  |  |  |

|              |      | 2.2.4 Platform modeling and deployment                  |  |  |  |  |  |

|              |      | 2.2.5 Analysis                                          |  |  |  |  |  |

| 3            | Sen  | sors and actuators in component-based development 25    |  |  |  |  |  |

|              | 3.1  | Effects of sensors and actuators on component-based de- |  |  |  |  |  |

|              |      | velopment                                               |  |  |  |  |  |

## x Contents

|          | 3.2   | .2 Modeling sensors and actuators in component-based ap-                      |     |  |  |  |

|----------|-------|-------------------------------------------------------------------------------|-----|--|--|--|

|          |       | proaches                                                                      | 27  |  |  |  |

|          |       | 3.2.1 Software layer                                                          | 28  |  |  |  |

|          |       | 3.2.2 Hardware layer                                                          | 30  |  |  |  |

|          |       | 3.2.3 Mapping layer                                                           | 31  |  |  |  |

|          |       | 3.2.4 Example                                                                 | 32  |  |  |  |

|          | 3.3   | Automatic synthesis of executable code                                        | 34  |  |  |  |

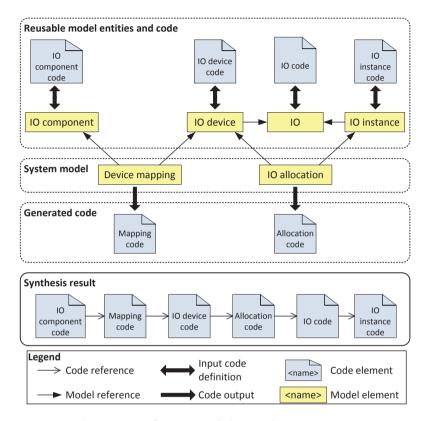

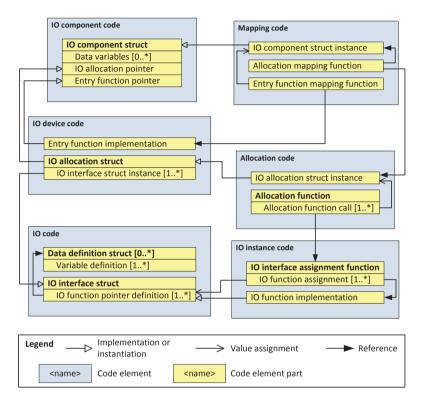

|          |       | 3.3.1 Input code definition                                                   | 36  |  |  |  |

|          |       | 3.3.2 Output code generation                                                  | 41  |  |  |  |

|          | 3.4   | Implementation and evaluation                                                 | 44  |  |  |  |

|          |       | 3.4.1 Implementation                                                          | 44  |  |  |  |

|          |       | 3.4.2 Evaluation                                                              | 44  |  |  |  |

|          | 3.5   | Summary                                                                       | 46  |  |  |  |

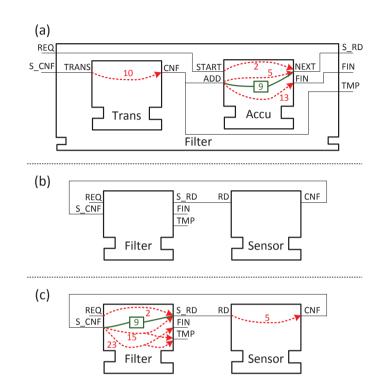

| 4        | A 111 | omatic generation of inter-node communication                                 | 49  |  |  |  |

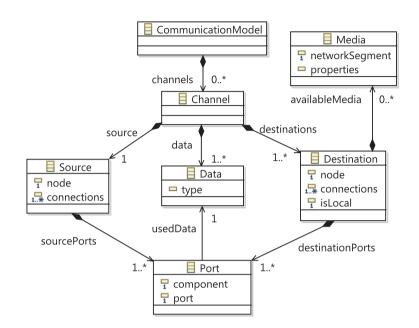

| -        | 4.1   | The communication model                                                       | 51  |  |  |  |

|          | 4.2   | Generation process                                                            | 53  |  |  |  |

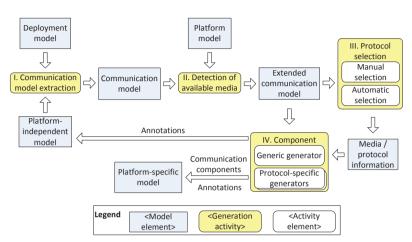

|          | 1.2   | 4.2.1 Communication model extraction                                          | 54  |  |  |  |

|          |       | 4.2.2 Communication model extraction                                          | 55  |  |  |  |

|          |       | 4.2.2     Protocol selection                                                  | 55  |  |  |  |

|          |       | 4.2.4 Communication component creation                                        | 56  |  |  |  |

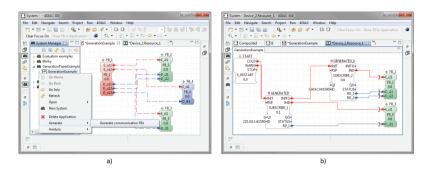

|          | 4.3   | IEC 61499 implementation of the framework                                     | 57  |  |  |  |

|          | 4.4   | Example and case-study                                                        | 60  |  |  |  |

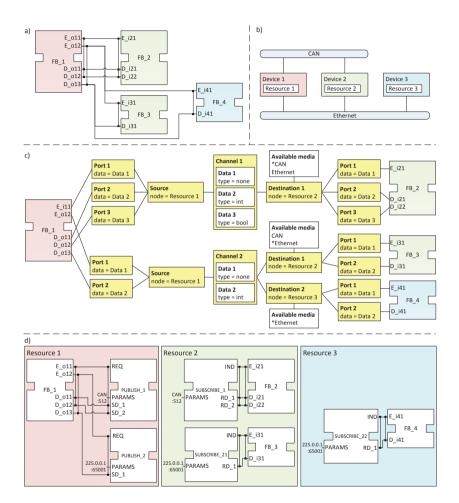

|          | 1.1   | 4.4.1 Example                                                                 | 60  |  |  |  |

|          |       | 4.4.2 Case-study evaluation                                                   | 62  |  |  |  |

|          | 4.5   | Summary                                                                       | 63  |  |  |  |

|          | 4.0   |                                                                               | 00  |  |  |  |

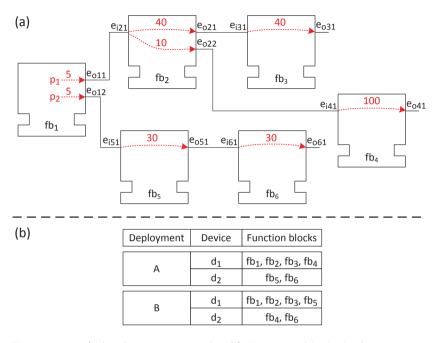

| <b>5</b> |       | 8                                                                             | 65  |  |  |  |

|          | 5.1   | Formal definition of IEC 61499                                                | 67  |  |  |  |

|          | 5.2   | WCET analysis of function blocks                                              | 69  |  |  |  |

|          |       | 5.2.1 WCET data definition $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 70  |  |  |  |

|          |       | 5.2.2 Data normalization                                                      | 74  |  |  |  |

|          |       | 5.2.3 Basic Function Block Analysis                                           | 75  |  |  |  |

|          |       | 5.2.4 Composite Function Block Analysis                                       | 79  |  |  |  |

|          | 5.3   | Handling cyclic execution paths                                               | 85  |  |  |  |

|          |       | 5.3.1 Cycle bound definition                                                  | 85  |  |  |  |

|          |       | 5.3.2 Cycle analysis                                                          | 88  |  |  |  |

|          |       | 5.3.3 Hierarchical propagation of cycle bounds                                | 95  |  |  |  |

|          | 5.4   | Analysis using hardware-specific models                                       | .00 |  |  |  |

|   |                                    | 5.4.1   | Device-specific WCET analysis 100                                                                           | ) |  |  |

|---|------------------------------------|---------|-------------------------------------------------------------------------------------------------------------|---|--|--|

|   |                                    | 5.4.2   | Application Analysis                                                                                        | 1 |  |  |

|   |                                    | 5.4.3   | Utilization analysis                                                                                        | 7 |  |  |

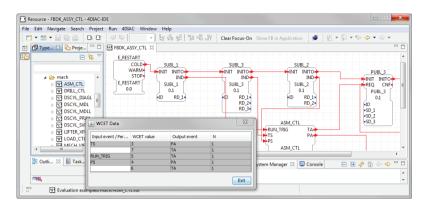

|   | 5.5                                | Implei  | nentation and evaluation $\ldots \ldots 109$ |   |  |  |

|   |                                    | 5.5.1   | Analysis tool                                                                                               | 9 |  |  |

|   |                                    | 5.5.2   | *                                                                                                           |   |  |  |

|   |                                    | 5.5.3   | Validation of cyclic path analysis                                                                          |   |  |  |

|   | 5.6                                |         | ary                                                                                                         |   |  |  |

| 6 | Related work 117                   |         |                                                                                                             |   |  |  |

|   | 6.1                                | Design  | and synthesis of hardware-                                                                                  |   |  |  |

|   |                                    | specifi | c code                                                                                                      | 7 |  |  |

|   | 6.2                                | Comm    | unication in distributed embedded systems 119                                                               | 9 |  |  |

|   | sis of extra-functional properties | 1       |                                                                                                             |   |  |  |

| 7 | Con                                | clusio  | n 125                                                                                                       | 5 |  |  |

|   | 7.1                                | Summ    | ary and discussion $\ldots \ldots 12$ | 5 |  |  |

|   | 7.2                                | Future  | e work                                                                                                      | 3 |  |  |

|   |                                    | 7.2.1   | Support for sensors and actuators                                                                           | 3 |  |  |

|   |                                    | 7.2.2   | Automatic generation of distributed communication 128                                                       | 3 |  |  |

|   |                                    | 7.2.3   | Analysis of extra-functional properties 129                                                                 | 9 |  |  |

|   |                                    |         |                                                                                                             |   |  |  |

## Bibliography

131

## Chapter 1

## Introduction

Almost all modern technology, from factories and vehicles, to consumer electronics and household appliances, is in some level supported by embedded computer systems. The increased usage of embedded systems has resulted in rapid growth of their complexity. An example of this can be seen in the automotive industry. Premium vehicles often have a hardware platform consisting of more than 100 processing units connected with multiple communication networks, running several thousands of software functions, and interact with the environment using numerous sensors and actuators [64]. Development of embedded systems is also complicated by the specifics of the embedded domain. The context they are used in often requires them to not only provide correct functionality, but to also deliver the functionality in a specific time. These systems also usually execute on platforms with limited resources, e.g. low processing power and memory capacity. As a result of these factors, it is getting harder to develop embedded software and ensure that the implementation satisfies its requirements. One of the possibilities for alleviating development of such complex systems is by applying model driven [7] and component-based [1, 17, 60] approaches for their development.

Model driven development advocates building systems by modeling them, and providing implementation by transforming models to executable code. This approach provides multiple benefits. The models provide a view of a system which is more abstract compared to executable code. Thus, much of the complexity of implementation can be hidden, and systems can be easier to develop and understand. The models used to create a system can also be used to analyze its various properties. Because it is applied to an abstract view of a system, model-level analysis can provide high efficiency, and is applicable in early stages of development, when the full implementation is not yet available. The ability to detect potential problems early can reduce the risk of costly redesign late in the development. A negative side of analysis on such abstract level is a possible decrease in the accuracy of results.

A system can often be described by more than one model. As an example, it is common to describe system functionality in a platformindependent manner, and provide the platform-specific details in a separate model. This allows each model to more clearly represent a specific aspect of the overall system. Also, besides just modeling software, some approaches include the ability to use models for describing the hardware platform that the software can be deployed to. However, having multiple coexisting models introduces the need of keeping them synchronized, and utilizing a combination of multiple models is not always trivial.

Model driven development is often combined with aforementioned component-based software engineering. In component-based software engineering systems are built by composing them out of software components – units of software which conform in their syntax and semantics to a component model.

The main characteristic of software components is that they are developed with reuse in mind. Component should implement a functionality which is independent to the context of a specific system, encapsulate that functionality, and provided it to the rest of the system only through a well-defined interface. The interface should also explicitly express all dependencies of a component, i.e. what functionality the component requires from the rest of the system. The benefit of component communicating only through a well defined interface is twofold. First, by having all components implement an interface conforming to same syntax and semantics it can be assured that different components can be composed together and exchange information. Second, the system developer can use components in a *black-box* manner, meaning that during component composition only components interfaces are used, while the complexity of the implementation stays hidden.

One problem which arises when applying component-based development in the embedded system domain is the tight coupling of software and hardware. The limited processing and memory resources often prevent use of extensive hardware abstraction layers usually present in the desktop domain. Because of this, the code implementing software components can become highly dependent on the hardware it communicates with. If not addressed properly, such dependencies can limit the potential of component reuse.

Besides promoting reuse, the previously mentioned encapsulation of component functionality also facilitates prediction of system properties. As the implementation of a component is isolated from the rest of the system, and ideally all components dependencies are explicitly expressed by the component interface, it becomes easier to predict properties of a single component. Then, in the same way that system functionality is built by composing functionality of components, the properties of a system can potentially be composed from properties of individual components. The increased predictability is one of the main benefits the component based approach can introduce to the development of embedded systems. It is, however, not trivial to define context-independent description of component properties and provide methods for composition of such properties, especially when considering the aforementioned tight coupling of software and hardware.

In this thesis we investigate how current state-of-the-art of componentbased development process can be advanced by leveraging software and hardware models of component-based systems. In the rest of this section we describe the research questions that have guided the research, present the main contributions of the thesis, list the publications which have been used as the basis for the thesis, describe the methodology used during research and in the end give an outline for the rest of the thesis.

## 1.1 Research questions

The overall goal of this research is to provide advancements in development of embedded component-based software systems by leveraging a combination of software and hardware models. To achieve this goal, we have investigated three aspects of component-based development for embedded systems consisting of software and hardware: (i) support for integrating sensors and actuators while modeling and deploying componentbased systems, (ii) development of distributed systems and (iii) analysis of extra-functional system properties. The conducted research has been guided by three research questions, which are presented below.

Interaction with the environment using IO devices such as sensors

and actuators is one of the key characteristics of embedded systems. The two most common ways for handling this interaction in componentbased development are to either make it a part of software component code, or let it be handled outside of the component model. Having the communication with IO devices encapsulated in software components hides the dependencies of components on the devices, and makes such components highly dependent on a specific hardware configuration. This breaks the principle of components having all dependencies expressed on the interface level and reduces the potential of component reuse. On the other hand, completely removing sensors and actuators from component models prevents the component-based design to cover the whole system and hides the effects of IO devices during system analysis. Such approach can thus reduce applicability of the component-based approach and predictability of systems. Therefore, we have defined the following research question:

**Research Question 1:** How can we improve the support for integration of sensors and actuators in component-based development for embedded systems, so that dependencies to these devices are more easily manageable?

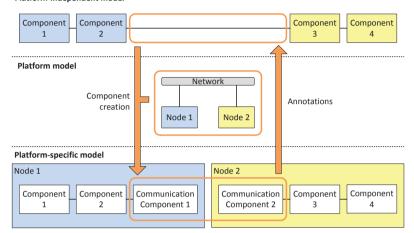

Some component models provide support for modeling distributed applications by providing two complementary sets of models: platformindependent models which abstract away from the details of communication between platform nodes, and platform-specific models which contain components that implement the distributed communication. Although the ability to model applications on these two levels can help coping with the complexity of distributed systems, manually keeping the two models synchronized is a time consuming and error-prone activity. Lack of established methods for keeping these models up-to-date in when using a component based approach led us to the second research question:

**Research Question 2:** How can we enhance development of distributed component-based systems in order to reduce the effort of synchronizing platform-independent and platform-specific models?

Embedded systems often have to satisfy domain-specific requirements such as real-time constraints. A common way of verifying if these requirements are met is through analysis. The fact that component-based systems are often built using abstract models provides a possibility for analysis to also be performed using these models. However, exploiting the full potential of model-level analysis in component-based systems is not trivial. This led us to define the following final research question:

**Research Question 3:** How can we utilize software and platform models to efficiently analyze extra-functional properties of componentbased systems in early stages of development?

## **1.2** Contributions

We have addressed the research questions presented in the previous section by the following four contributions.

**Research contribution 1 (RC1):** Component-based embedded system model with integrated sensors and actuators.

We have extended the ProCom component model [53] with an ability to describe IO devices (i.e. sensors and actuators) that are part of the hardware platform, and means to specify how these devices are connected to the processing nodes of the platform. The new model lets software components state their dependencies on specific types of IO devices on the level of component interface, and allows these dependencies to be propagated through component hierarchy. During the deployment phase, the dependencies of software components can be mapped to the available IO devices. The proposed approach promotes reuse by having context-independent model elements loosely bound and clearly separated from the system-specific ones. A part of the contribution is also a prototype modeling tool implementing the approach. The contribution was evaluated by applying it to a realistic example, proving that the models adequately describe the system.

**Research contribution 2 (RC2):** Code synthesis method based on the proposed component model.

We have developed a method that provides automatic generation of platform specific code for transfer of data between software components and IO devices (i.e. sensors and actuators). The generation leverages the platform model which describes IO devices, processing nodes, how the two are connected, and how the software components communicate with IO devices. The method defines how to specify reusable code segments for context-independent model elements, and generates glue-code connecting these segments into a system-specific solution. The generation method is implemented for the ProCom component model and supported by a prototype tool. The synthesis method has been evaluated in combination with RC1 by applying the prototype tool to a realistic example. The results of the evaluation proved that the synthesized code correctly implements system functionality. A part of the evaluation was also measuring the overhead of the generated code in terms of execution time and memory footprint.

**Research contribution 3 (RC3):** Method for automatic generation of communication components in distributed embedded systems models.

We have defined a framework which supports automatic generation of communication between nodes of distributed component-based applications. The generation uses platform-independent software models and models of the platform to insert and configure components which implement the required communication. The framework introduces adaptability and extensibility by separating generation into different loosely bound modules connected only through well-defined interfaces. The method has been applied to the IEC 61499 standard and implemented in a prototype tool. The contribution has been evaluated by applying it to an extended example, and two case-study systems. The evaluation showed that the generated models were in line with the expected results, and that the generated communication correctly implements the functionality of the case-study systems.

### **Research contribution 4 (RC4):** Method for compositional timing and utilization analysis of component-based systems.

We have developed a novel method for timing analysis of componentbased embedded software systems built using the IEC 61499 standard. The analysis method relies on the concepts of component composition and hierarchy to provide efficient calculation of worst-case execution time for composite components and applications. By extending the timing analysis to use a combination of software and platform models, we have enabled analysis of processing resource utilization. Both timing and utilization analysis have been implemented in a prototype tool. The prototype tool was used to evaluate the analysis using a set of example models taken from two IEC 61499 development tools, and a set of test scenarios. The evaluation using example models proved that the analysis is applicable to realistic systems, and that the performance of the analysis algorithms is high. Applying the analysis on the set of test scenarios has validated the correct behavior of parts of the analysis method.

## 1.3 Research methodology

The research method applied to the work presented in this thesis generally aligns to the engineering version of the scientific method given by Basili [5]: "observe existing solutions, propose better solutions, build/develop, measure and analyze, and repeat the process until no more improvements". The overall research has been conducted according to following steps:

- 1. Investigation of state-of-the-art and state-of-the-practice in the field of component-based software engineering for embedded systems.

- 2. Definition of a concrete research problem, followed by an in-depth literature review and definition of a research goal.

- 3. An iterative process of: (i) development of a theoretical research result, (ii) implementation of a prototype tool, (iii) evaluation of the method using the prototype tool.

- 4. Validation of the method using a case-study or a set of tests.

As we have addressed multiple concrete problems, all the steps have been performed for each problem separately.

The research started with a survey of component-based models developed for use in the embedded system domain [19]. As a part of the survey, we have identified a lack of support for expressing the interaction with the hardware platform in such development approaches, with the automatic generation of hardware-specific code as a possibility of improvement. The research continued with a more thorough analysis of existing approaches for modeling hardware. Based on this, we have defined a method to model sensors and actuators in component models for embedded systems. The modeling method was then used to provide the method of automatic generation of sensor- and actuator-specific code.

The part of the research that addresses system analysis started with a project which included transfer of research applied conducted in scope of the ProCom component-model to the more industrial setting of the IEC 61499 standard [15]. Based on the existing model-level analysis for ProCom [13] and an investigation of other existing methods for both model- and code-level timing analysis we proposed a novel method for timing analysis which could take advantage of the specifics of componentbased development approach. The results of this research were then combined with the results of the research on hardware modeling, and the new analysis method was extended to take into account models of both software and hardware. As we have identified the lack of support analysis of cyclic execution paths to be a problem in current model-level analysis methods, we have also extended the timing analysis with an ability to analyze such constructs.

During the research on model-level analysis, we also identified a possibility of enhancing the analysis method by performing the analysis on platform-specific models which include inter-node communication components. As we did not find a component-based development framework which would allow generating such model from platform-independent models and model of the platform, we extended our research to provide such a method.

For each new method we defined, we developed the theoretical contributions in parallel with a prototype tool. The tools were used to evaluate the applicability of the methods, and iteratively updating the methods using the insights gained by the evaluation.

The presented work is validated through persuasion, examples and evaluation, as defined by Shaw [54]. When possible, a *slice of life* example is used, rather than a *toy example*. To some extent, the developed tools are been applied to the examples to provide a more detailed information about the performance of proposed methods, rather than just test their applicability.

## 1.4 Publications

This section first presents the main publications contributing to this thesis, and then lists the rest of the related publications.

### 1.4.1 Main contributing publications

The publications presented in this section constitute the basis for this doctoral thesis. For all these publications I am the main author of both

contributions and text, while other coauthors contributed with smaller amounts of text, and valuable discussions and reviews.

• Paper A: Adding Support for Hardware Devices to Component Models for Embedded Systems, Luka Lednicki, Juraj Feljan, Jan Carlson, Mario Žagar, The Sixth International Conference on Software Engineering Advances (ICSEA), 2011.

This paper introduces a possibility of modeling sensors and actuators, describing how they are connected with processing nodes of the platform, and specifying their interaction with software components, providing contribution RC1. The work presented in this paper is the basis for a part of Chapter 3 where the approach for modeling sensors and actuators is described.

• Paper B: Automatic Synthesis of Hardware-specific Code in Component-based Embedded Systems, Luka Lednicki, Ivica Crnković, Mario Žagar, The Seventh International Conference on Software Engineering Advances, 2012.

In this paper the results of Paper A have been used to define a method for synthesis of code that connects software components to sensors and actuators. The method specifies how to define reusable code elements and allows automatic generation of glue-code between these elements, resulting in contribution RC2. The part of Chapter 3 that concerns code synthesis is based on this paper.

• Paper C: A Framework for Generation of Inter-node Communication in Component-based Distributed Embedded Systems, Luka Lednicki, Jan Carlson, IEEE International Conference on Emerging Technology and Factory Automation, 2014.

This paper presents an extensible framework which allows automatic generation of communication between nodes of distributed systems by adding communication components to platform-specific system models, providing contribution RC3. Paper C is used as the basis for Chapter 4. • Paper D: Model Level Worst-case Execution Time Analysis for IEC 61499, Luka Lednicki, Jan Carlson, Kristian Sandström, The 16th International ACM Sigsoft Symposium on Component-based Software Engineering, 2013.

The contribution of this paper is a novel method for compositional worst-case execution time analysis of component-based software, giving the foundation for the thesis contribution RC4. This paper is used as the basis for a part of Chapter 5, where the model level timing analysis for IEC 61499 is introduced.

• Paper E: Device Utilization Analysis for IEC 61499 Systems in Early Stages of Development, Luka Lednicki, Jan Carlson, Kristian Sandström, IEEE International Conference on Emerging Technology and Factory Automation, 2013.

In this paper we extend the analysis method described in Paper C to utilize models of hardware platform to provide a novel method for analyzing device utilization, adding to contribution RC4. The paper is used as the basis for the part of Chapter 5 describing processing node utilization analysis.

• **Paper F:** Handling Cyclic Execution Paths in Timing Analysis of Component-based Software, Luka Lednicki, Jan Carlson, The 40th Euromicro Conference on Software Engineering and Advanced Applications, 2014. (short paper)

This paper further extends the analysis method presented in Paper C with the ability to analyze software models of component-based applications which contain cyclic execution paths, further extending contribution RC4. Paper F is the basis for the analysis of cyclic paths in IEC 61499 given in Chapter 5.

All of the main contributing papers are used as a partly basis for the background presented in Chapter 2 and the related work described in Chapter 6.

## 1.4.2 Other related publications

### Peer reviewed publications

• 15 Years of CBSE Symposium: Impact on the Research Community, Josip Maras, Luka Lednicki, Ivica Crnković, Proceedings of the 15th ACM SIGSOFT Symposium on Component-based Software Engineering, 2012.

- Towards Automatic Synthesis of Hardware-specific Code in Component-based Embedded Systems, Luka Lednicki, Ivica Crnković, Mario Žagar, Proceedings of the 38th Euromicro Conference on Software Engineering and Advanced Applications, 2012. (short paper)

- PRIDE an Environment for Component-based Development of Distributed Real-time Embedded Systems, Etienne Borde, Jan Carlson, Juraj Feljan, Luka Lednicki, Thomas Leveque, Josip Maras, Ana Petričić, Séverine Sentilles, 9th Working IEEE/IFIP Conference on Software Architecture, 2011.

- Support for Hardware Devices in Component Models for Embedded Systems, Luka Lednicki, International Doctoral Symposium on Software Engineering and Advanced Applications, 2011.

- DICES: Distributed Component-based Embedded Software Systems, Mario Žagar, Ivica Crnković, Darko Stipaničev, Maja Štula, Juraj Feljan, Luka Lednicki, Josip Maras, Ana Petričić, Annual of the Croatian Academy of Engineering, 2010/2011.

- A Component-Based Technology for Hardware and Software Components, Luka Lednicki, Ana Petričić, Mario Žagar, 35th Euromicro Conference on Software Engineering and Advanced Applications, 2009. (short paper)

- Using UML for Domain-specific Component Models, Ana Petričić, Luka Lednicki, Ivica Crnković, Fourteenth International Workshop on Component-oriented Programming, 2009.

- Uniform Treatment of Hardware and Software Components, Luka Lednicki, Jan Carlson, Mario Žagar, 8th Conference on Software Engineering Research and Practice in Sweden, 2008.

#### Technical reports

• Feasibility of Migrating Analysis and Synthesis Mechanisms from ProCom to IEC 61499, Jan Carlson, Luka Lednicki, MRTC report, 2012.

• Classification and Survey of Component Models, Juraj Feljan, Luka Lednicki, Josip Maras, Ana Petričić, Ivica Crnković, MRTC report, 2009.

## 1.5 Thesis outline

In this section we give an outline to the rest of the thesis chapters.

#### Chapter 2 – Background

The chapter gives an overview of the existing concepts and research needed to understand the contributions presented in the thesis. The overview consists of descriptions of the ProCom component model and the IEC 61499 standard.

### Chapter 3 – Sensors and actuators in component-based development

This chapter first discusses effects that sensors and actuators have on component-based development process, and then introduces an extension to the ProCom component model which allows modeling of sensors and actuators, and in the end describes the method for synthesis of sensorand actuator-specific code. The work presented in this chapter is based on Paper A [43] and Paper B [41] of the main contributing publications of the thesis, and [42]. This chapter updates the modeling approach described in the publications, introduces a common example model for the modeling and synthesis contribution, and extends the evaluation of the approach.

### Chapter 4 – Automatic generation of inter-node communication

We describe a framework for automatic generation of communication in distributed component-based applications. In the chapter we first introduce a model which captures communication requirements of applications. After that we describe the process of automatic generation of distributed communication. In the end we exemplify the generation on a simple model. The contributions of this chapter are based on Paper C [36] of the main contributing publications. Apart from improved descriptions, this chapter does not add to the work presented in the Paper C.

#### Chapter 5 – Model-level timing and utilization analysis

In this chapter we present a novel model-level analysis method for analysis of component-based systems. First, we introduce a method for compositional analysis of worst-case execution time of component-based software applications. We then describe how the compositional analysis can be applied to applications which contain cyclic execution paths. We complete the chapter with a method for analysis of processing node utilization which is based on the compositional worst-case execution time analysis. This chapter is based on the main contributing publications Paper D [40], Paper E [39] and Paper F [37]. The descriptions and formal definitions presented in the publications are improved, and new formal definitions are added to the previous work.

#### Chapter 6 – Related work

We provide an overview if existing research that is related to the work presented in this thesis.

#### Chapter 7 – Conclusion

This chapter concludes the thesis.

## Chapter 2

# Background

This chapter describes the ProCom component model and the IEC 61499 standard. The presentation of ProCom is kept on a higher level, sufficient to understand the work presented in Chapter 3, and mainly describes how some of the common component-based development concepts are implemented by this component model. The IEC 61499 standard is described on a more detailed level, as the contributions in Chapter 4 and Chapter 5 are more closely connected to the details of the standard.

## 2.1 ProCom

ProCom [10, 11, 53] is a component model for development of safetycritical distributed embedded real-time systems. One of the main aims of ProCom is to provide component-based approach that covers the whole development process, including design, analysis and deployment of systems. Development of ProCom systems is supported by the open-source PRIDE tool [8]. The rest of this section gives an overview of various parts of the ProCom approach.

### 2.1.1 Components

ProCom has a strong notion of components, which are rich and reusable design-time entities. Each component implements a specific functionality, encapsulates it, and provides it only through a well-defined interface.

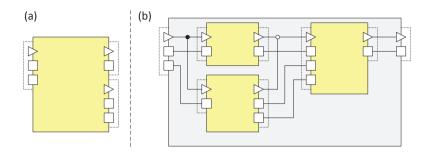

Figure 2.1: (a) ProSave component interface. The triangles and squares represent trigger and data ports, respectively. While the input ports are located on the left border of the components, the output ports are located on the right side. Port groups are denoted by dashed lines encompassing the ports. (b) An example of a composite ProSave component.

Besides their functionality, components can also store various other elements, for example behavior models or property values. Syntax and semantics of components is defined on the interface level. This allows treatment of components in a black-box manner, promoting their reuse. Although ProCom provides two modeling levels, ProSave and ProSys, each with different levels of component granularity, for the purpose of this thesis we will only concentrate on the lower, ProSave layer.

On the ProSave level, systems are modeled by connecting components in a pipe-and-filter manner, with clear distinction between the data and control flow. On the interface level, ProSave components<sup>1</sup> consist of one input port group, and zero or more output port group. Each group contains one trigger port and an arbitrary number of data ports. The trigger ports of a component are used to activate the execution of the component (input trigger) or send activation signals to other components (output trigger), while the data ports are used to send or receive data. The graphical representation of a ProSave component on the interface level is given in Figure 2.1 (a).

<sup>&</sup>lt;sup>1</sup>For the purpose of this thesis, the notion of ProSave *service*, and the ability of components to provide multiple input port groups, will be disregarded.

#### 2.1.2 Component types

Based on how they implement their functionality, ProSave distinguishes two types of components: primitive components and composite components. The implementation of primitive components is defined by code, with each component defining an entry function in C language which will be executed when the component is triggered. Composite components implement their functionality using interconnected subcomponents. In this way, functionality provided by a composition of components can be encapsulated and presented in a black-box manner, as a component, and reused on higher levels of hierarchy. Figure 2.1 (b) shows an example of the interface and implementation of a ProSave composite.

#### 2.1.3 Semantics

All types of ProSave components adhere to same semantics, defined on the level of the component interface [59,66]. The components are passive, meaning that they never start execution unless activated by a signal at their input trigger port. Once triggered for execution, components follow a read-execute-write pattern. First, the values at the input ports of the interface are read and transferred to the component's internal implementation. Then, the functionality of the component is executed. During the execution, the output data ports are updated with new values, and activation signals are sent through output trigger ports. Output of the data and the triggering signal for each group is performed as an atomic operation. When all output triggers of a component have been activated, the component stops its execution and remains inactive until the next activation of its input trigger port.

#### 2.1.4 Platform modeling and deployment

ProCom supports modeling of execution platforms and how software systems are deployed to those platforms [14]. Models of hardware platforms consist of physical nodes and network connections between them. Physical nodes represent concrete hardware processing units. Deployment of software systems to the platform is done by mapping the software components to the physical nodes<sup>2</sup>.

$<sup>^2\</sup>mathrm{In}$  the work presented in this thesis, the ProCom concept of virtual nodes is disregarded.

#### 2.1.5 Analysis

One of the main aspects of ProCom is aim to support analysis of system properties. The support for attaching attributes or models, which can be used for analysis, is given by an extensive framework for specification of extra-functional properties [52]. Besides providing support for attaching extra-functional properties to components, various analysis techniques have been developed in the context of ProCom, for example analysis of timing properties [13, 44], and resource usage analysis [51, 65].

## 2.2 IEC 61499

The IEC 61499 standard [28,61,67,70] is proposed as a successor of the IEC 61131-3 standard [27], which is widely used in industry, especially for development of industrial automation systems. The new standard addresses some of the problems of IEC 61131-3, mainly focusing on enhancing reusability, configurability, interoperability, reconfiguration and support for distributed systems. Development using IEC 61499 is supported by several tools, for example 4DIAC [56], Function Block Development Kit [24], nxtStudio [47] and ISaGRAF [26]. The details of the component-based approach of IEC 61499 are described in the following sections.

#### 2.2.1 Components

The software components of the IEC 61499 standard are called *function* blocks. As is common in component-based approaches, the functionality of a function block is presented by the *function block interface*, which hides the details of the implementation. Similarly to ProCom (described in Section 2.1), the IEC 61499 function block interface explicitly separates event and data inputs and outputs. Event inputs and outputs are used to specify the execution flow, but do not provide any means for exchanging data between function blocks. All data transfers are done by data inputs and outputs.

Relations between event and data ports can be described by WITH qualifiers. A WITH qualifier can be defined on either a combination of one input event port and a set of data inputs, or one output event port and a set of data outputs. Defining a WITH qualifier on an event input port and a set of data input ports describes which data inputs will

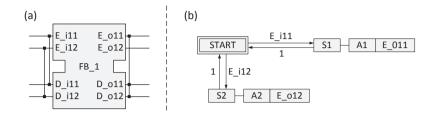

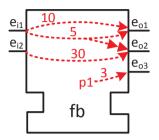

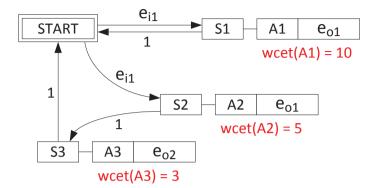

Figure 2.2: (a) An IEC 61499 function block interface. (b) A basic function block ECC.

be sampled together with the event port. A WITH qualifier combining an event output port with a set of data output ports shows which data outputs will be updated with new values together with an output at the event output.

**Example:** Figure 2.2 (a) shows an example of a function block interface, defined for function block  $FB_{-1}$ . The figure shows a function block with input event ports  $E_{-i11}$  and  $E_{-i12}$ , output event ports  $E_{-o11}$  and  $E_{-o12}$ , data inputs  $D_{-i11}$  and  $D_{-i12}$ , and data outputs  $D_{-o11}$  and  $D_{-o12}$ . The WITH qualifiers are represented by connecting the ports with vertical lines, marking each port belonging to a WITH qualifier by a black rectangle. As an example, the WITH operator defined on the outputs of FB implies that when an event is generated on  $E_{-o11}$ , the values on ports  $D_{-o11}$  and  $D_{-o12}$  will also be updated.

#### 2.2.2 Component types

Considering their implementation, function blocks can be of three possible types: Basic function block, Service interface function block and Composite function block.

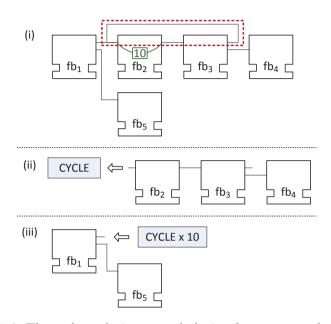

A basic function block (BFB) is implemented by means of an *Execu*tion Control Chart (ECC) and one or more algorithms. The ECC is an automaton consisting of states and guarded transitions. Each state can be associated with zero or more actions. An action can specify one or more algorithms which will be executed once the state is reached, and output event ports that will be activated. We differentiate between two types of states: stable states in which execution of the ECC stops until a new event arrives at an input port, and transitional states which do not require an event for ECC to move to another state. Execution of basic function blocks is strictly event driven - it can only start when an event is received at one of the input ports, and once the execution stops it will not continue until the next event arrives. One execution cycle of a function block is called a *run*. A single run can traverse more than one ECC state in case the ECC contains transitional states, and thus result in an arbitrary number of algorithm executions and output events.

**Example:** An example of a basic function block ECC is given in Figure 2.2 (b). It contains states START, S1 and S2, with START being the initial state. The transition from START to S1 is guarded by the input event  $E_{-i11}$ . When this state is reached, algorithm A1 is executed, and an event is generated at output event port  $E_{-o11}$ . The transition to state S2 is guarded by the input event  $E_{-i12}$ , and it executes algorithm A2 and outputs an event at  $E_{-i12}$ . Both S1 and S2 are transitional states – there are transitions back to START that are not guarded by any event, depicted by a 1 as the transition condition.

Service interface function blocks (SIFB) are designed to be used as interfaces to external hardware or services. The functionality of this element is not specified by the standard, and although they can contain a sequence diagram describing their behavior, the functionality might not be fully documented. Unlike basic function blocks, the service interface function blocks can start their execution without the arrival of an input event (active execution).

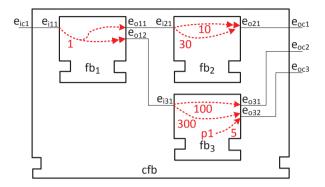

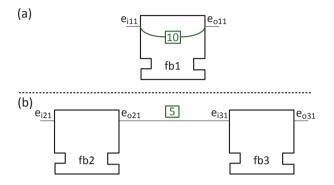

A composite function block (CFB) has an implementation defined by a function block network (defined below), with additional connections between the ports of the enclosing interface and the ports of the function blocks in the network. As the composite function block can contain active service interface function blocks, composites can also be active, i.e. start their execution without receiving an input event.

A function block network (FBN) defines the internal structure of a composite function block or a whole application. A function block network consists of a set of function blocks of arbitrary types (BFB, SIFB or CFB) and connections between the ports of these function blocks. As a result of the separation of event and data ports, the flow of control and data are clearly distinguished.

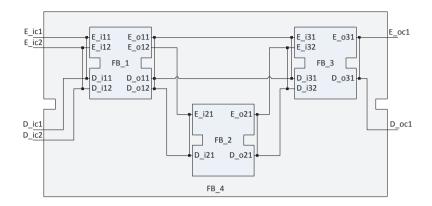

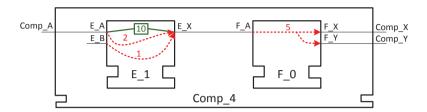

**Example:** An example of a composite function block, named  $FB_{-4}$ , can be seen in Figure 2.3. Its internal function block network contains three function blocks,  $FB_{-1}$ ,  $FB_{-2}$ , and  $FB_{-3}$ .

Figure 2.3: A composite function block with an internal function block network.

#### 2.2.3 Semantics

Unlike the previously described ProCom component model, the semantics of IEC 61499 function blocks is not unambiguously defined on the level of component interface [57, 58]. While basic function blocks are strictly passive, starting their execution only by receiving signals to their input event ports, and following a read-execute-write pattern, service interface function blocks can also start their execution by means of an internal trigger. Both of these function block types, regardless of their triggering, are executed as atomic units: no other function block will interrupt their execution. As composites can contain both these types of function blocks, they can also be either passive or active components. The definition of composites also does not clearly define the atomicity of their execution. The standard does not specify if it should be allowed to interrupt execution of a composite function block by some function block outside of the composite. As a result, different IEC 61499 implementations provide different semantics for composites, and it is harder to argue about properties of function block compositions. Although not defined by the standard itself, a formal definition of execution semantics [63] has been published in the research community.

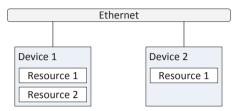

Figure 2.4: Example model of the platform in IEC 61499.

#### 2.2.4 Platform modeling and deployment

In IEC 61499 the platform is represented by *devices*. A device is an independent physical entity capable of performing one or more specified functions. Each device contains one or more *resources*, which are functional units with independent control of operation.

Communication networks between devices are modeled by *network* segments. One device can be connected to more than one segment, and there is no limit to the number of devices that can be connected to a single network segment.

**Example:** Figure 2.4 shows an example of platform model consisting of two devices connected via an Ethernet network segment. *Device 1* has two resources, and *Device 2* with only one resource.

Applications are deployed to the platform by mapping its function blocks to the resources contained in the devices. Since all function blocks, including composites, are atomic units of deployment, each function block can be mapped to only one resource.

Each resource in a distributed IEC 61499 system contains a local model of the application, containing only the subset of the application's function blocks which are mapped to that particular resource. This local model can however contain additional function blocks which are not visible on the application level. It is a common practice to use this option to implement functionality that is specific to the current mapping of the application, such as adding inter-resource communication function blocks.

#### 2.2.5 Analysis

Analysis was not one of the original main concerns of IEC 61499, and analysis of IEC 61499 models has not yet been fully explored [67,70]. One of the obstacles for performing analysis on the level of IEC 61499 models is also the previously mentioned ambiguity of execution semantics. Some of the analysis techniques developed for IEC 61499 are described as part of the related work, in Section 6.3.

The IEC 61499 standard allows attaching properties to modeling elements in form of attributes. The types of attributes are not defined in advance – they can hold any information about functional or extrafunctional properties of the model elements. The standard also supports inheritance of attributes, for example function block instances inherit attributes from their respective function block types.

# Chapter 3

# Sensors and actuators in component-based development

One of the main characteristics of embedded systems is their interaction with the environment using sensors and actuators. The communication between software components and such IO devices can be as simple as writing a value to a hardware pin or a port, or as complex as invoking a service on a remote device. In all cases, this interaction introduces dependencies of software on the underlying hardware used to interact with the environment. The same interaction can also affect behavior and properties of software components, as, for example, properties like data acquisition time can vary for different types of sensors. Failure to adequately express this interaction can result in models that do not capture all system properties, and reduce the potential of component reuse, thus hindering the full utilization of the component-based approach in the embedded system domain.

In this chapter, we will first describe the effects that sensors and actuators can have on model-driven component-based development process, and then present our approach for modeling sensors and actuators in component-based systems and a method which allows automatic synthesis of code based on the proposed models. The chapter continues with description of a prototype tool which implements the presented methods and provides information about the evaluation, and ends with a summary. The work presented in this chapter is based on Paper A [43] and Paper B [41] of the main contributing publications of the thesis, and [42].

## 3.1 Effects of sensors and actuators on component-based development

When applying a model-driven component-based software engineering approach to embedded systems, the dependencies of software components on sensors and actuators, as well as communication between the software and hardware, impacts multiple aspects of the development process. In this section we will give an overview of some of them.

When *designing* a system, the developer specifies the system using models of (i) the software layer of the system, as a composition of software components, and (ii) the hardware platform layer, as a composition of nodes that the system will be deployed to. The former requires means to manage interaction with sensors and actuators in the software layer, i.e. to specify which components communicate with IO devices, and how. The latter calls for an ability to describe actual instances of sensors and actuators, and how they are connected to processing nodes of the platform. Additionally, if we want to accommodate to the component *reuse* concept, it must be ensured that the components dependent on sensors and actuators can be deployed to various hardware platforms.

During system *deployment* the components of the software layer are allocated to the elements of the platform layer that will execute them. In this phase, there is a need to identify the dependencies of the software components on sensors and actuators in order to ensure that the platform elements targeted for deployment satisfy these dependencies.

To guarantee that the system satisfies its requirements, the developer can perform various types of *analysis*. Such analysis can be used to check both functional and extra-functional properties of a system. For the results of the analysis to be valid, the effects of interaction of software components with sensors and actuators must be taken into account.

Finally, in the *synthesis* phase system models are used to generate executable code. In this phase, it must be ensured that the generated code reflects the specifics of the platform and correctly implements the communication with sensors and actuators.

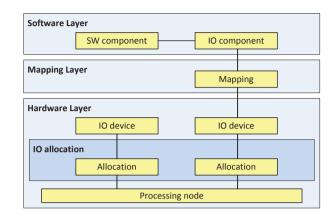

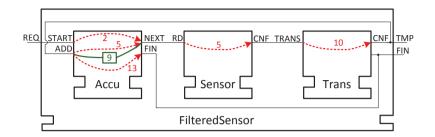

Figure 3.1: Overview of the layered model for describing IO devices in component based development.

# 3.2 Modeling sensors and actuators in component-based approaches

To address the problem of specifying the interaction of software components with sensors and actuators we have defined a model which allows incorporation of sensors and actuators into component models, and applied it to ProCom.

To limit the amount of coupling between software components and IO devices we have separated the model into three layers: *software layer*, *hardware layer* and *mapping layer*. With this separation the software and the hardware of the system can be described independently, making the descriptions suitable for reuse in different scenarios. When developing a concrete system, the independent software and hardware layers can be connected using the mapping layer. The same principle of loose binding that is introduced by the mapping layer is also used in the hardware layer, where connections between processing nodes and IO devices are defined by IO allocations. An abstract overview of these three layers is given in Figure 3.1.

The IO device modeling approach introduces a clear distinction between *types* and *instances* for both hardware and software entities. Types are entity definitions that are context-independent. They can be reused in different settings or stored in repositories for future use. To use a type in a concrete system, an instance of that type needs to be created. In this case instances are not copies of the entity, but rather representatives of the general entity in a specific context. For example, when describing an IO device, the description actually defines a type. When creating a system containing the IO device, a developer creates a new instance of that type. In some cases, instances can also refine properties of the type depending on the usage context.

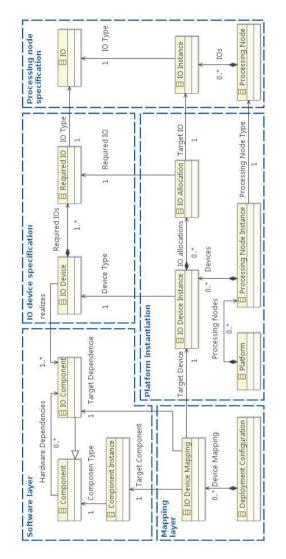

The next three sections give a detailed description of the model layers, referencing the metamodel given in Figure 3.2. The metamodel is defined using Ecore, a language for describing metamodels provided by the Eclipse Modeling Framework [55].

#### 3.2.1 Software layer

To enable describing interaction of component-based applications with IO devices, we have introduced a new type of component – IO component. This component type is derived from ordinary software component, providing the same interface and adhering to the same execution semantics. The difference between normal software components and IO components is in their internals. Device components do not provide an ability for developers to explicitly specify their realization, and do not contain any device specific code (e.g. code for actual communication with hardware). This is because they inherit their realization from IO devices once the two are mapped together (described in detail in Section 3.2.3).

To be able to use device components in composites, and still treat composites in a black-box manner, components have to specify their device dependencies on the interface level. Therefore we have also extended the component interface with a device dependency list, containing references to device components. In case of device components this list always contains only one entry, referencing the device component itself. Primitive components which are implemented by code always have an empty IO dependency list. For composite components, the device dependency list matches the combined dependencies of all of its subcomponents. It should be noted that primitive and composite types of components are not covered by the meta-model in Figure 3.2.

3.2 Modeling sensors and actuators in component-based approaches 29

Figure 3.2: Ecore metamodel that defines the model for including sensors and actuators in component models.

#### 3.2.2 Hardware layer

The hardware layer allows describing processing nodes that runnable code can be deployed to, IO devices such as sensors and actuators, and platforms which consist of instances of processing nodes and IO devices. As reuse is one of the main characteristics of component-based approach, the hardware layer model is also defined in a manner which promotes reuse. It consists of three separate logical parts: *processing node specification*, *IO device specification* and *platform instantiation*. In the following sections we will go into the details of these three.

#### Processing node specification

*Processing nodes* describe hardware which can be a target for deployment of executable code, for example microcontroller or ECUs. They are reusable model entities as they only describe types of nodes, and do not contain any information about how nodes are used or configured in a particular system.

Processing nodes define a list of inputs and outputs they provide using *IO instances*. Each IO instance references an IO type (e.g. one-bit digital I/O, serial communication port, analog input, etc.).

Processing nodes and their inputs and outputs can also be characterized by extra-functional properties such as their processing power, available memory, behavioral models, delays for input and output functions and other similar attributes.

#### **IO** device specification

*IO Devices* represent sensors and actuators that can be connected to processing nodes in order to interact with the environment. Like processing nodes, device definitions are reusable and define a type of sensor or actuator, rather than an actual instance.

Each IO device references an IO component type for which the device can be used as realization. It should be noted that one IO component type can be referenced by many different devices. For example, a temperature sensor device can be referenced by two different temperature sensor implementations (i.e. IO devices). However, a device component in the software layer does not depend on these particular implementations. Similarly to the list of inputs and outputs provided by processing nodes, devices define a list of inputs and outputs that they require for communication.

Devices also support defining attributes that describe their extrafunctional properties.

#### **Platform** instantiation

As opposed to processing nodes and devices, platforms represent particular hardware configurations which are not aimed for reuse. They are defined as sets of processing node and device instances, each instance referencing its type.

Besides defining instances of processing nodes and devices, the platform instantiation also describes how each device instance is connected to a processing node instance. This is done using *IO allocation* model entities. Each IO allocation references an IO instance of a processing node and a required IO of a device, denoting to which inputs or outputs, and how, a sensor or actuator is connected. Once that allocation of inputs and outputs is defined, the platform can also be checked to determine if IO requirements of all device instances are fulfilled by the processing nodes they are attached to.

#### 3.2.3 Mapping layer

As already stated, the software and hardware model layers are defined in manner which reduces their interdependency to a minimum, therefore promoting reuse of structures defined in them. The mapping layer allows defining a set of *IO device mappings* which reference an IO component in the software layer and an IO device instance in the hardware layer. Each mapping denotes which sensor or actuator will be used as implementation for an IO component. By this, reusable units of the two layers are put in the context of a system.

A mapping between an IO component and an IO device can be created only if the type of the device instance references the type of the IO component instance. This constraint ensures that a system is deployed in a valid way.

The approach supports IO device mappings to be defined even in early stages of system development, before the full implementation is complete. This, for example, allows early analysis of system properties using the combination of software and hardware layers.

#### 3.2.4 Example

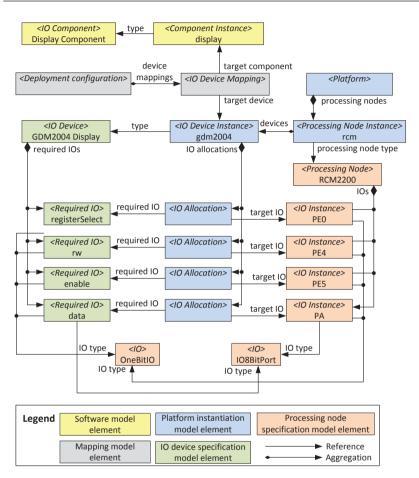

To illustrate use of the proposed modeling approach, it will be demonstrated on an example. The example model, shown in Figure 3.3, describes a simple system that consists of an IO component for output to a display, a GDM2004 display device and an RCM2200 microcontroller. It should be noted that the example does not capture all functionality or hardware provided by the display or the microcontroller, but only the parts needed to demonstrate the approach.

The IO device component for communication with a hardware display provides interface for showing text messages. For this, the component receives as input the message text, and position, in rows and columns, where the message should appear.

The GDM2004 display provides only textual output capabilities, having four lines with 20 character columns each. The characters are sent to the display one at a time by writing data to a data register, with each character printed at the position defined by the inner state of the display, described by a cursor. The position of the cursor can be set at any time by writing data to a control register, and is increased by one column after each character write.

For the purpose of the example, the RCM2200 microcontroller will provide two ports, PA and PE, which can be either used for parallel 8-bit input or output, or as 8 separate single-bit inputs or outputs.

Processing node specification defines reusable model elements which describe processing nodes, IO types, and IO instances provided by processing nodes. In this example, processing node specification consist of a single processing node type, the *RCM2200* microcontroller, and two IO types: *OneBitIO* which sends or receive s single bit value from a hardware pin, and *IO8BitPort* which can be used to send or receive eight bits in parallel through eight hardware pins. To describe the communication capabilities of the microcontroller, *RCM2200* contains four IO instances: *PE0*, *PE4* and *PE5* of type *OneBitIO*, and *PA* of type *IO8BitPort*.